# zilog

# **Z8 Family of Microcontrollers**

Z8<sup>®</sup> CPU

**User Manual**

UM001604-0108

Warning: DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8 is the registered trademark of Zilog, Inc. All other product or service names are the property of their respective owners.

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date              | Revision<br>Level | Description                                                                      | Page No   |

|-------------------|-------------------|----------------------------------------------------------------------------------|-----------|

| January<br>2008   | 04                | Updated Zilog logo, Zilog text, Disclaimer section, and implemented Style Guide. | All       |

| February<br>2007  | 03                | Changed the OP code to B0 and B1 in Instruction Description.                     | 167       |

| September<br>2004 | 02                | Formatted to current publication standards.                                      | All pages |

UM001604-0108 Revision History

# **Table of Contents**

| Z8 <sup>®</sup> CPU Product Overview       |

|--------------------------------------------|

| Key Features                               |

| Product Development Support                |

| Address Space                              |

| Introduction                               |

| Z8 <sup>®</sup> CPU Standard Register File |

| General-Purpose Registers                  |

| RAM Protect                                |

| Working Register Groups                    |

| Error Conditions                           |

| Z8 Expanded Register File                  |

| Z8® Control and Peripheral Registers       |

| Standard Z8 Registers                      |

| Expanded Z8 Registers                      |

| Program Memory                             |

| Z8® External Memory                        |

| External Data Memory                       |

| Z8® Stacks                                 |

|                                            |

| Clock                                      |

| Frequency Control                          |

| Clock Control                              |

| SCLK ÷ TCLK Divide-By-16 Select            |

| External Clock Divide-By-Two               |

| Oscillator Control                         |

| Oscillator Operation                       |

| Layout 28                                  |

| Indications of an Unreliable Design        |

| Circuit Board Design Rules                 |

| Crystals and Resonators                    |

| LC Oscillator 3 <sup>-</sup>               |

| RC Oscillator                              |

| Reset                                      |

| Reset Pin, Internal POR Operation          |

| ·                                          |

| Watchdog Timer                             |

UM001604-0108 Table of Contents

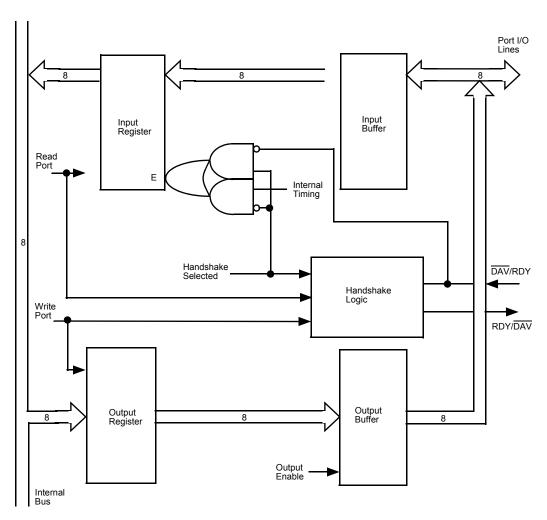

| Input/Output Ports            |    |

|-------------------------------|----|

| Mode Registers                |    |

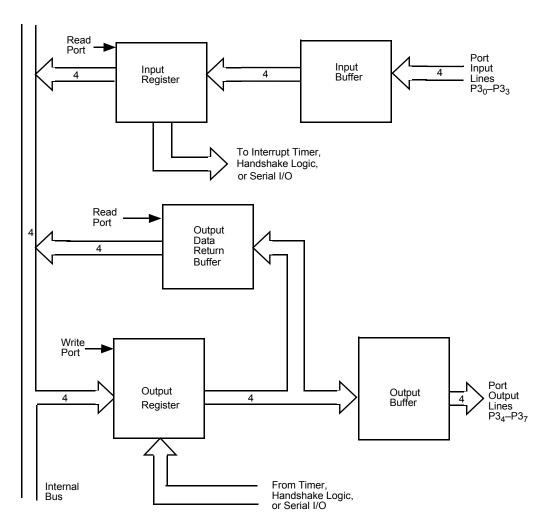

| Input and Output Registers    |    |

| Port 0                        |    |

| General I/O Mode              |    |

| Read/Write Operations         |    |

| Handshake Operation           |    |

| Port 1                        |    |

| General I/O Mode              |    |

| Read/Write Operations         |    |

| Handshake Operations          |    |

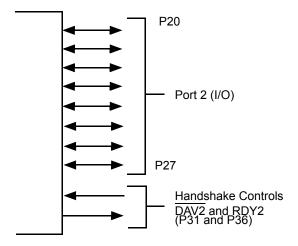

| Port 2                        |    |

| General Port I/O              |    |

| Read/Write Operations         |    |

| Handshake Operation           |    |

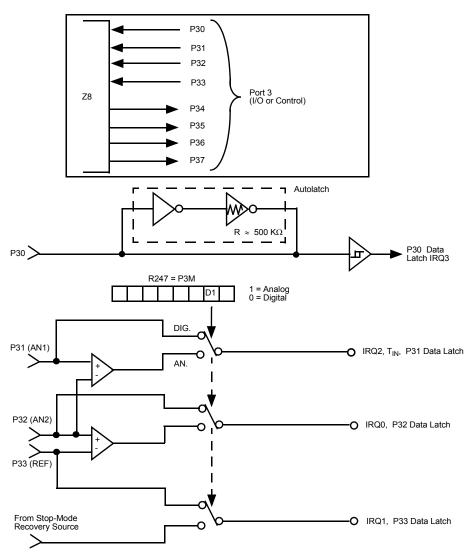

| Port 3                        |    |

| General Port I/O              |    |

| Read/Write Operations         |    |

| Special Functions             |    |

| Port Handshake                |    |

| I/O Port Reset Conditions     |    |

| Full Reset                    |    |

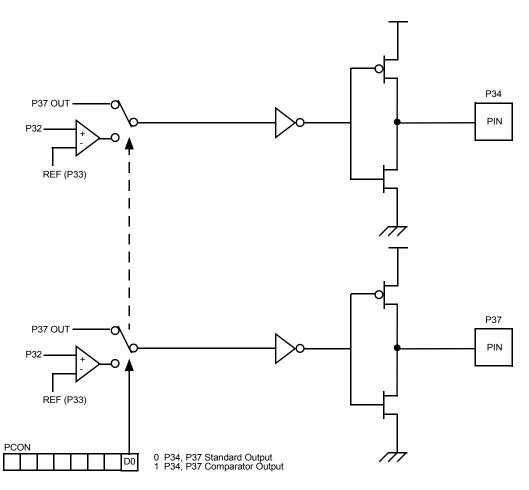

| Analog Comparators            |    |

| Comparator Description        |    |

| Comparator Programming        |    |

| Comparator Operation          |    |

| Interrupts                    |    |

| Comparator Definitions        |    |

| Run Mode                      |    |

| Halt Mode                     |    |

| Stop Mode                     |    |

| Open-Drain Configuration      |    |

| Low EMI Emission              |    |

| Z8® CMOS Autolatches          |    |

| Autolatch Model               |    |

|                               |    |

| Design Considerations         |    |

| Counters and Timers           |    |

| Prescalers and Counter/Timers |    |

| Counter/Timer Operation       |    |

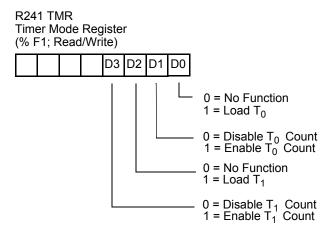

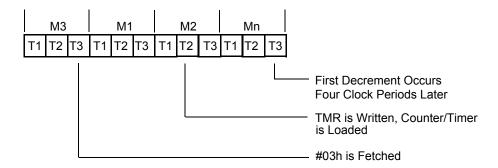

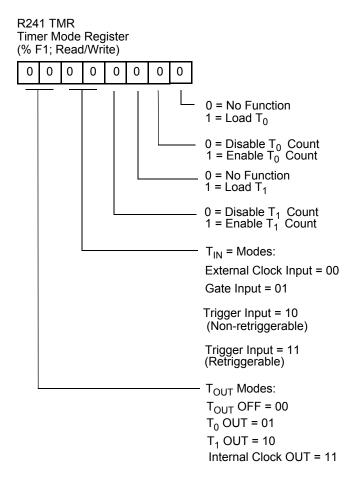

| Load and Enable Count Bits    | 83 |

UM001604-0108 Table of Contents

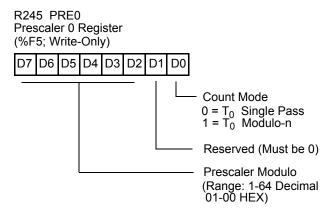

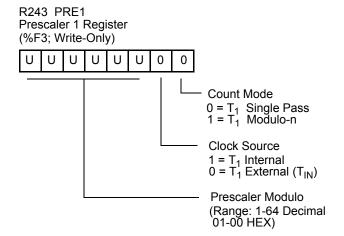

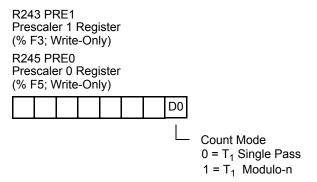

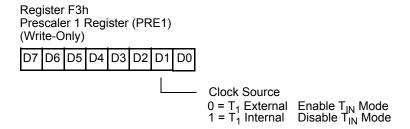

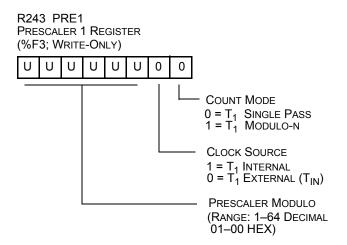

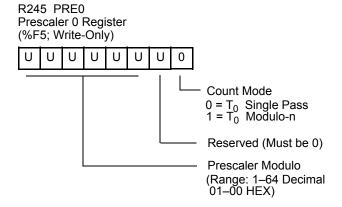

| Prescaler Operations                        | 84  |

|---------------------------------------------|-----|

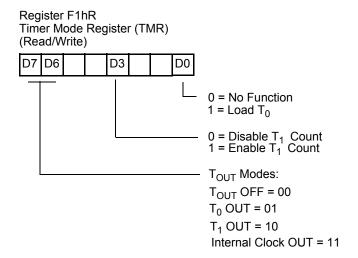

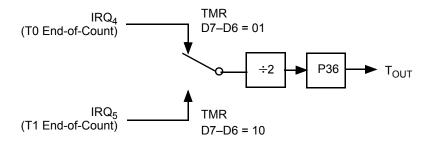

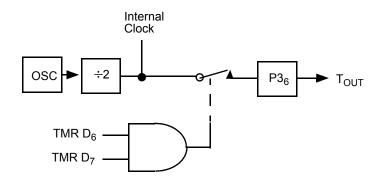

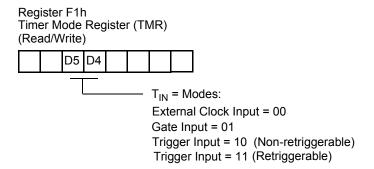

| T <sub>OUT</sub> Modes                      | 86  |

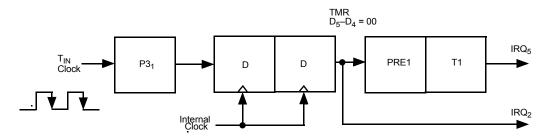

| T <sub>IN</sub> Modes                       |     |

| External Clock Input Mode                   | 89  |

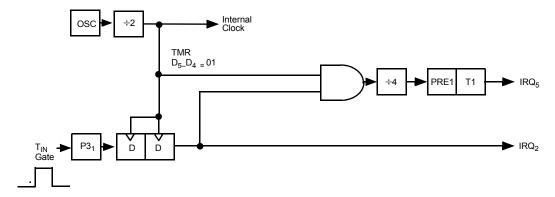

| Gated Internal Clock Mode                   | 90  |

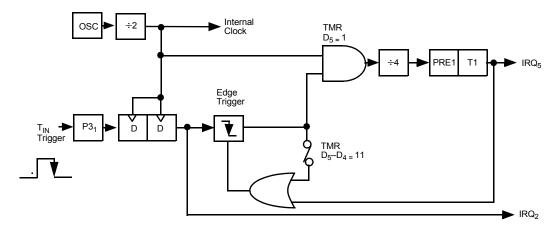

| Triggered Input Mode                        | 90  |

| Retriggerable Input Mode                    |     |

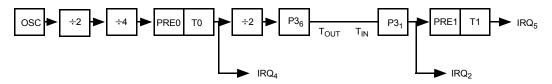

| Cascading Counter/Timers                    |     |

| Reset Conditions                            |     |

| Interrupts                                  |     |

| ·                                           |     |

| Interrupt Sources                           |     |

| External Interrupt Sources                  |     |

| Internal Interrupt Sources                  |     |

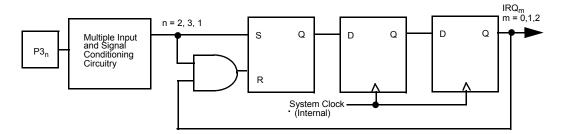

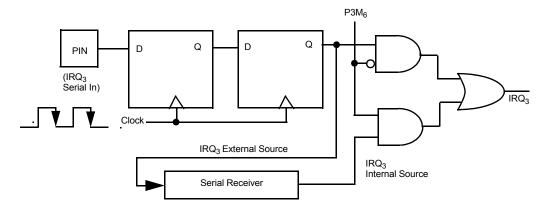

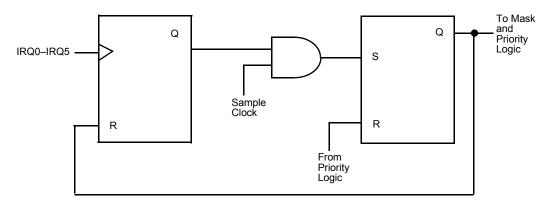

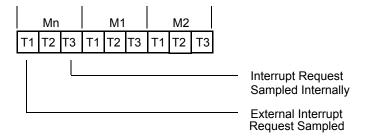

| Interrupt Request Register Logic and Timing |     |

| Interrupt Initialization                    |     |

| Interrupt Priority Register Initialization  |     |

| Interrupt Mask Register Initialization      |     |

| Interrupt Request Register Initialization   |     |

| IRQ Software Interrupt Generation           |     |

| Vectored Processing                         |     |

| Vectored Interrupt Cycle Timing             |     |

| Nesting of Vectored Interrupts              |     |

| Polled Processing                           |     |

| Reset Conditions                            | 109 |

| Power-Down Modes                            | 110 |

| Halt Mode Operation                         | 110 |

| Stop Mode Operation                         | 110 |

| Stop Mode Recovery Register                 | 112 |

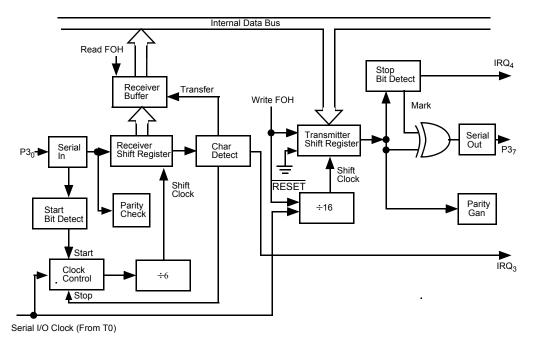

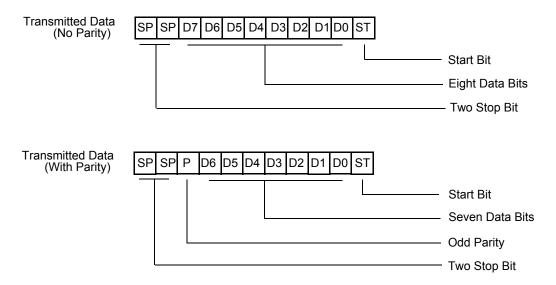

| Serial Input/Output                         |     |

| UART Introduction                           |     |

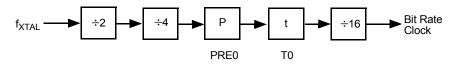

| UART Bit-Rate Generation                    |     |

| UART Receiver Operation                     |     |

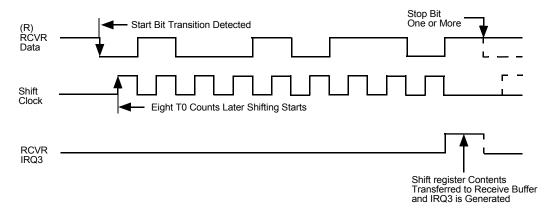

| Receiver Shift Register                     |     |

| Overwrites                                  | _   |

|                                             |     |

| Framing Errors                              | _   |

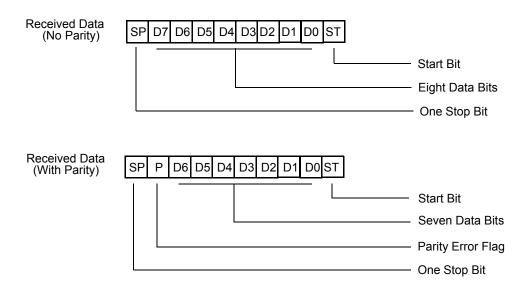

| Parity                                      |     |

| Transmitter Operation                       |     |

| Overwrites                                  |     |

| Parity                                      |     |

| UART Reset Conditions                       | 122 |

UM001604-0108 Table of Contents

| `\' |   |

|-----|---|

| v   | ı |

| Serial Peripheral Interface                                                                                                                                                                                |                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| SPI Compare                                                                                                                                                                                                |                                                                    |

| SPI Clock                                                                                                                                                                                                  |                                                                    |

| Receive Character Available and Overrun                                                                                                                                                                    |                                                                    |

| External Interface                                                                                                                                                                                         | 131                                                                |

| Introduction                                                                                                                                                                                               |                                                                    |

| Pin Descriptions                                                                                                                                                                                           | 131                                                                |

| External Addressing Configuration                                                                                                                                                                          | 132                                                                |

| External Stacks                                                                                                                                                                                            | 133                                                                |

| Data Memory                                                                                                                                                                                                | 134                                                                |

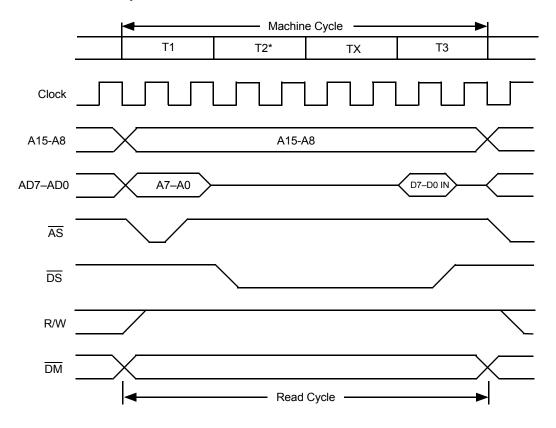

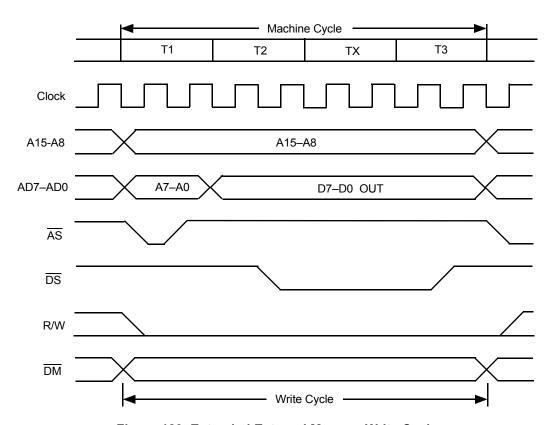

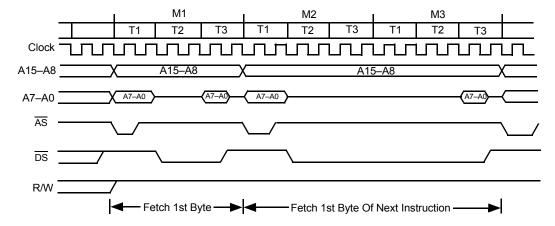

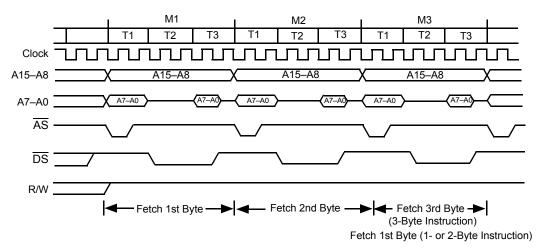

| Bus Operation                                                                                                                                                                                              | 134                                                                |

| Address Strobe                                                                                                                                                                                             | 136                                                                |

| Data Strobe                                                                                                                                                                                                | 136                                                                |

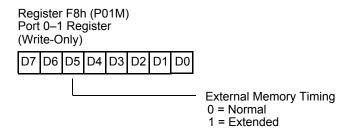

| Extended Bus Timing                                                                                                                                                                                        | 137                                                                |

| Instruction Timing                                                                                                                                                                                         |                                                                    |

| Z8 <sup>®</sup> Reset Conditions                                                                                                                                                                           | 140                                                                |

|                                                                                                                                                                                                            |                                                                    |

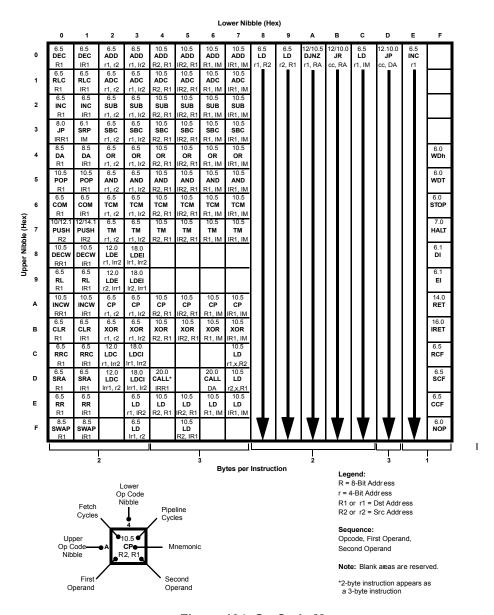

| Instruction Set                                                                                                                                                                                            | 141                                                                |

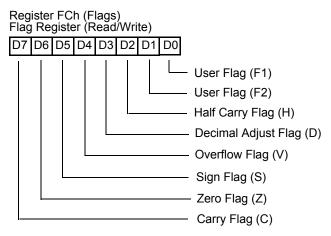

| Processor Flags                                                                                                                                                                                            |                                                                    |

|                                                                                                                                                                                                            | 144                                                                |

| Processor Flags                                                                                                                                                                                            | 144<br>144                                                         |

| Processor Flags                                                                                                                                                                                            | 144<br>144<br>145                                                  |

| Processor Flags                                                                                                                                                                                            | 144<br>144<br>145<br>145                                           |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag                                                                                                                           | 144<br>145<br>145<br>145<br>145<br>145                             |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag Half Carry Flag                                                                                                           | 144<br>145<br>145<br>145<br>145<br>146                             |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag Half Carry Flag Condition Codes                                                                                           | 144<br>145<br>145<br>145<br>145<br>146                             |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag Half Carry Flag Condition Codes Notation and Binary Encoding                                                              | 144<br>145<br>145<br>145<br>145<br>146<br>146<br>147               |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag Half Carry Flag Condition Codes Notation and Binary Encoding Assembly Language Syntax                                     | 144<br>145<br>145<br>145<br>145<br>146<br>146<br>147               |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag Half Carry Flag Condition Codes Notation and Binary Encoding Assembly Language Syntax Z8® Instruction Summary             | 144<br>145<br>145<br>145<br>145<br>146<br>146<br>147<br>149<br>150 |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag Half Carry Flag Condition Codes Notation and Binary Encoding Assembly Language Syntax                                     | 144<br>145<br>145<br>145<br>145<br>146<br>146<br>147<br>149<br>150 |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag Half Carry Flag Condition Codes Notation and Binary Encoding Assembly Language Syntax Z8® Instruction Summary             | 144<br>145<br>145<br>145<br>146<br>146<br>147<br>149<br>150        |

| Processor Flags Carry Flag Zero Flag Sign Flag Overflow Flag Decimal Adjust Flag Half Carry Flag Condition Codes Notation and Binary Encoding Assembly Language Syntax Z8® Instruction Summary Op Code Map | 144<br>145<br>145<br>145<br>146<br>146<br>147<br>149<br>150<br>156 |

UM001604-0108 **Table of Contents**

# **Z8<sup>®</sup> CPU Product Overview**

Zilog's Z8<sup>®</sup> microcontroller (MCU) product line continues to expand with new product introductions. Zilog MCU products are targeted for cost-sensitive, high-volume applications including consumer, automotive, security, and HVAC. It includes ROM-based products geared for high-volume production (where software is stable) and one-time programmable (OTP) equivalents for prototyping as well as volume production where time to market or code flexibility is critical (see Table 1 on page 3). A variety of packaging options are available including plastic DIP, SOIC, PLCC, and QFP.

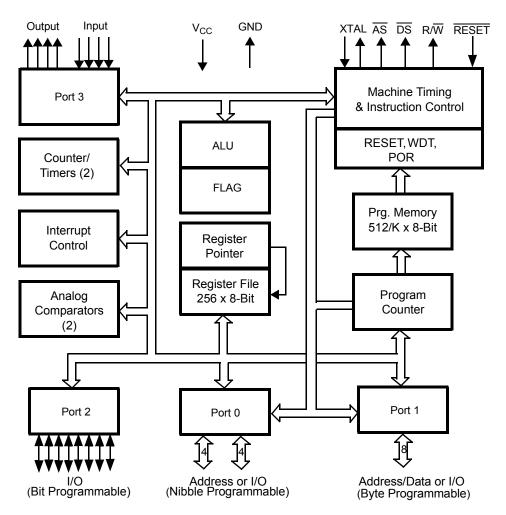

A generalized Z8 CPU block diagram is displayed in Figure 1 on page 2. The same onchip peripherals are used across the MCU product line with the primary differences being the amount of ROM/RAM, number of I/O lines present, and packaging/temperature ranges available. This allows code written for one MCU device to be easily ported to another family member.

### **Key Features**

The key features include:

**General-Purpose Register File—**Every RAM register acts like an accumulator, speeding instruction execution and maximizing coding efficiency. Working register groups allow fast context switching.

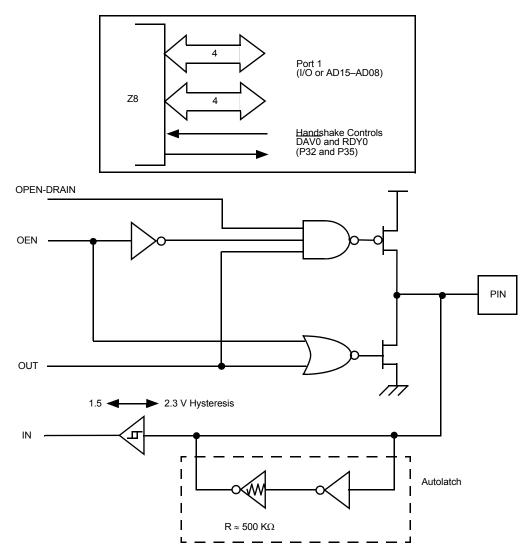

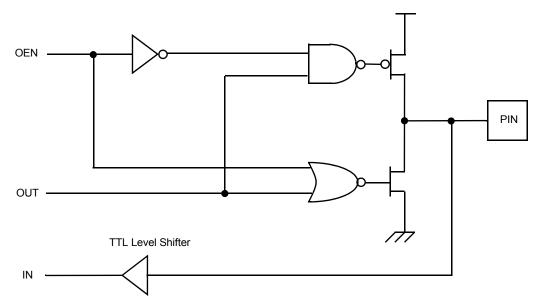

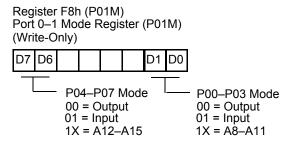

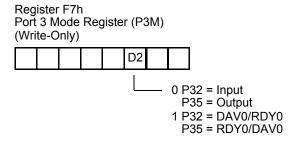

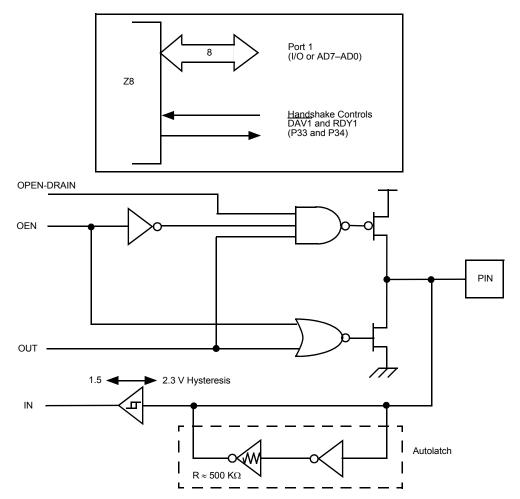

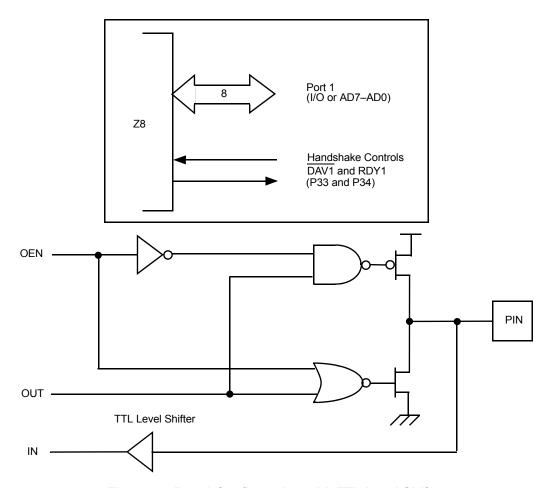

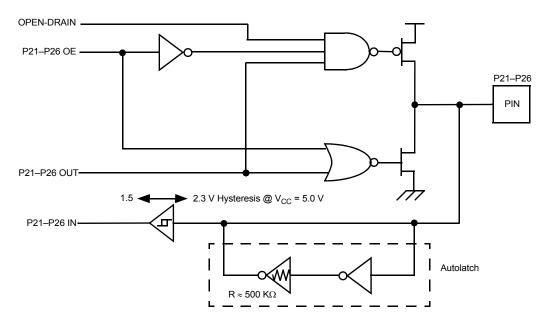

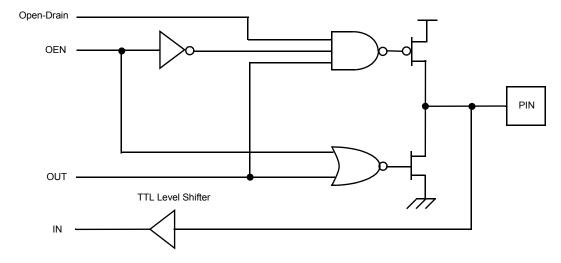

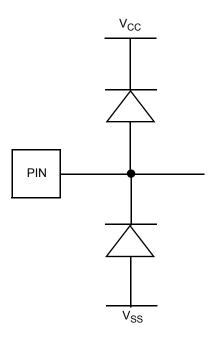

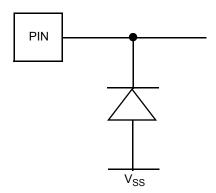

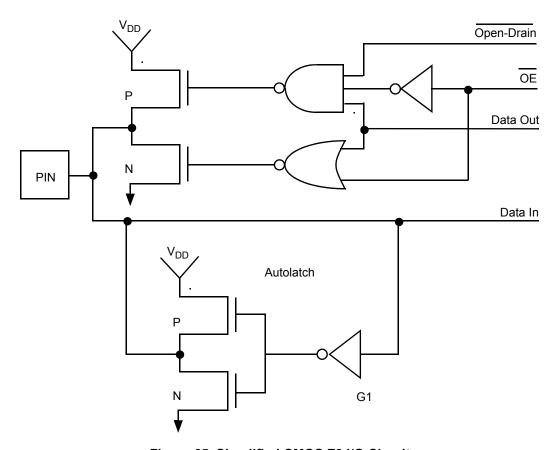

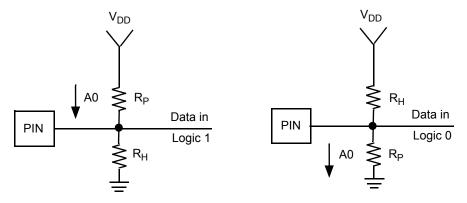

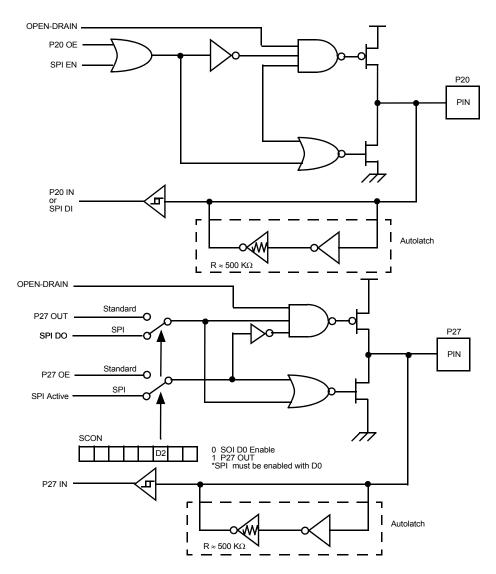

**Flexible I/O—**I/O byte, nibble, and/or bit programmable as inputs or outputs. Outputs are software programmable as open-drain or push–pull on a port basis. Inputs are Schmitt-Triggered with autolatches to hold unused inputs at a known voltage state.

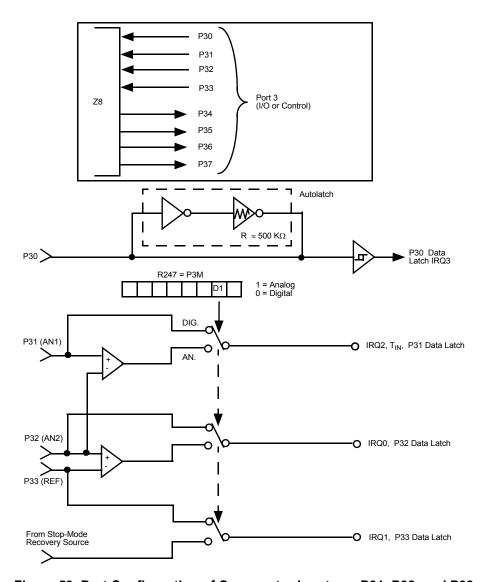

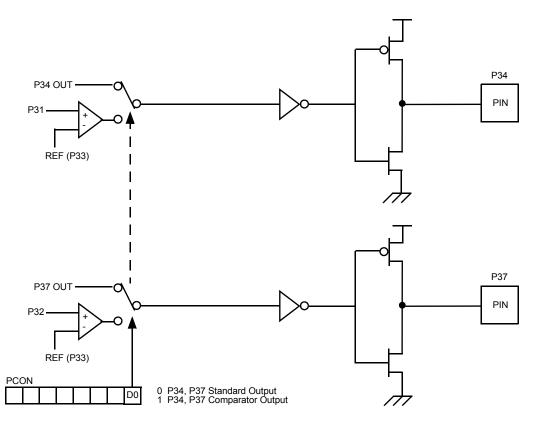

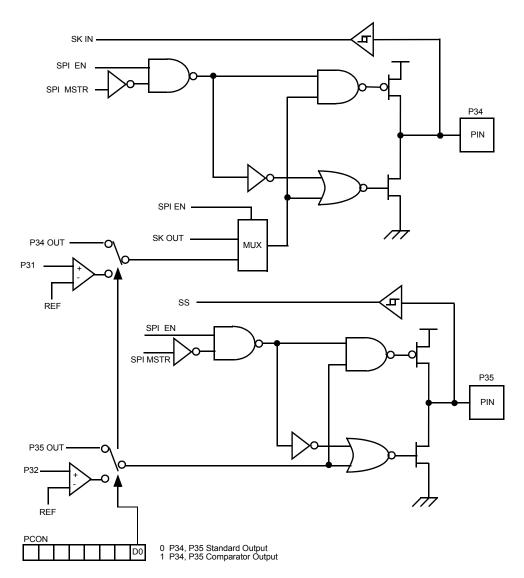

**Analog Inputs**—Three input pins are software programmable as digital or analog inputs. When in analog mode, two comparator inputs are provided with a common reference input. These inputs are ideal for a variety of common functions, including threshold level detection, analog-to-digital conversion, and short circuit detection. Each analog input provides a unique maskable interrupt input.

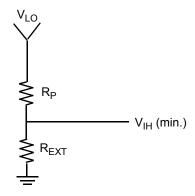

**Timer/Counter**—The Timer/Counter (T/C) consists of a programmable 6-bit prescaler and 8-bit downcounter, with maskable interrupt upon end-of-count. Software controls T/C load/start/stop, countdown read (at any time on the fly), and maskable end-of-count interrupt. Special functions available include  $T_{\rm IN}$  (external counter input, external gate input, or external trigger input) and  $T_{\rm OUT}$  (external access to timer output or the internal system clock). These special functions allow accurate hardware input pulse measurement and output waveform generation.

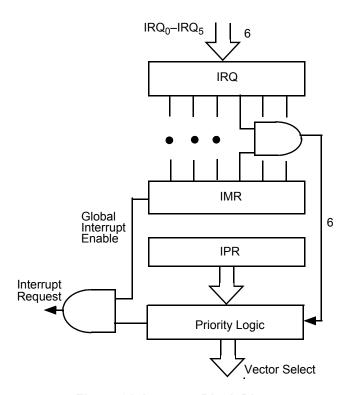

**Interrupts—**There are six vectored interrupt sources with software-programmable enable and priority for each of the six sources.

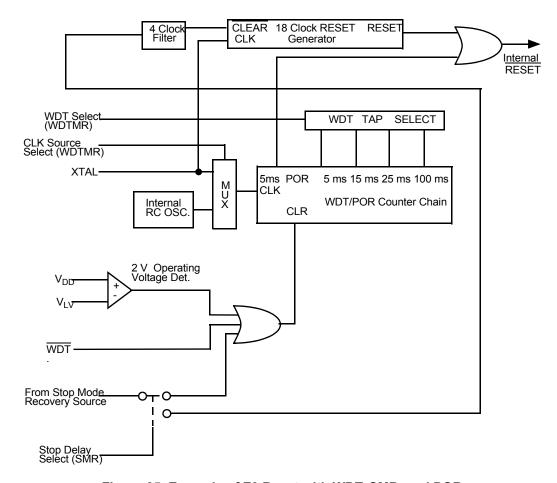

**Watchdog Timer**—An internal Watchdog Timer (WDT) circuit is included as a fail-safe mechanism so that if software strays outside the bounds of normal operation, the WDT is used to time-out and reset the MCU. To maximize circuit robustness and reliability, the

default WDT clock source is an internal RC circuit (isolated from the device clock source).

**Auto Reset/Low-Voltage Protection**—All family devices have internal Power-On Reset. ROM devices add low-voltage protection. Low-voltage protection ensures the MCU is in a known state at all times (in active RUN or RESET modes) without external hardware (or a device reset pin).

**Low-EMI Operation**—Mode is programmable via software or as a mask option. This new option provides for reduced radiated emission via clock and output drive circuit changes.

Low-Power—CMOS with two standby modes; STOP and HALT.

**Full Z8**<sup>®</sup> **Instruction Set**—Forty-eight basic instructions, supported by six addressing modes with the ability to operate on bits, nibbles, bytes, and words.

Figure 1. Z8 CPU Block Diagram

### **Product Development Support**

The  $Z8^{\mathbb{R}}$  MCU product line is fully supported with a range of cross assemblers, C compilers, ICEBOX emulators, single and gang OTP/EPROM programmers, and software simulators.

The Z86CCP01ZEM low-cost Z8 CCP real-time emulator/programmer kit is designed specifically to support all the products outlined in Table 1 on page 3.

**Table 1. Zilog General-Purpose Microcontroller Product Family**

| Product | ROM/<br>RAM | I/O | T/C | AN | INT | WDT | POR | $V_{BO}$ | RC | Speed<br>(MHz) | Pin<br>Count |

|---------|-------------|-----|-----|----|-----|-----|-----|----------|----|----------------|--------------|

| Z86C03  | 512/60      | 14  | 1   | 2  | 6   | F   | Υ   | Υ        | Υ  | 8              | 18           |

| Z86E03  | 512/60      | 14  | 1   | 2  | 6   | F   | Υ   | N        | Υ  | 8              | 18           |

| Z86C04  | 1K/124      | 14  | 2   | 2  | 6   | F   | Υ   | Υ        | Υ  | 8              | 18           |

| Z86E04  | 1K/124      | 14  | 2   | 2  | 6   | F   | Υ   | N        | Υ  | 8              | 18           |

| Z86C06  | 1K/124      | 14  | 2   | 2  | 6   | Р   | Υ   | Υ        | Υ  | 12             | 18           |

| Z86E06  | 1K/124      | 14  | 2   | 2  | 6   | Р   | Υ   | N        | Υ  | 12             | 18           |

| Z86C08  | 2K/124      | 14  | 2   | 2  | 6   | F   | Υ   | Υ        | Υ  | 12             | 18           |

| Z86E08  | 2K/124      | 14  | 2   | 2  | 6   | F   | Υ   | N        | Υ  | 12             | 18           |

| Z86C30  | 4K/236      | 24  | 2   | 2  | 6   | Р   | Υ   | Υ        | Υ  | 12             | 28           |

| Z86E30  | 4K/236      | 24  | 2   | 2  | 6   | Р   | Υ   | N        | Υ  | 12             | 28           |

| Z86C31  | 2K/124      | 24  | 2   | 2  | 6   | Р   | Υ   | Υ        | Υ  | 8              | 28           |

| Z86E31  | 2K/124      | 24  | 2   | 2  | 6   | Р   | Υ   | N        | Υ  | 8              | 28           |

| Z86C40  | 4K/236      | 32  | 2   | 2  | 6   | Р   | Υ   | Υ        | Υ  | 16             | 40/44        |

| Z86E40  | 4K/236      | 32  | 2   | 2  | 6   | Р   | Υ   | N        | Υ  | 16             | 40/44        |

**Note:** Z86Cxx signify ROM devices; 86xx signify EPROM devices; F = fixed; P = programmable.

#### The Z86CCP01ZEM kit includes:

- Z8 CCP evaluation board

- Z8 CCP power cable

- Zilog Developer Studio (ZDS) CD-ROM, Including Windows-Based GUI Host Software

- 1999 Zilog Technical Library

- Z8 CCP User Manual

A Z8 CCP Emulator Accessory Kit (Z8CCP00ZAC) is also available and provides an RS-232 cable and power cable along with the 28- and 40- pin ZIF sockets and 28- and 40-pin target connector cables required to emulate/program 28-/40-pin devices.

# **Address Space**

#### Introduction

$Z8^{\circledR}\,\text{CPU}$  includes the following four address spaces:

- The Z8 Standard Register File contains addresses for peripheral, control, all general-purpose, and all I/O port registers. This is the default register file specification.

- The Z8 Expanded Register File (ERF) contains addresses for control and data registers for additional peripherals/features.

- Z8 external Program Memory contains addresses for all memory locations having executable code and/or data.

- Z8 external data memory contains addresses for all memory locations that hold data only, whether internal or external.

# Z8® CPU Standard Register File

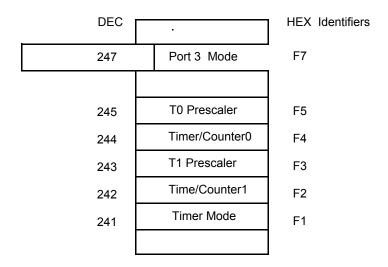

The Z8 Standard Register File totals up to 256 consecutive bytes (Registers). The register file consists of 4 I/O ports (00h-03h), 236 General-Purpose Registers (04h-EFh), and 16 control registers (F0h-FFh). Table 2 lists the layout of the register file, including register names, locations, and identifiers.

Table 2. Z8 Standard Register File

| Hex Address | Register<br>Identifier | Register Description        |

|-------------|------------------------|-----------------------------|

| FF          | SPL                    | Stack Pointer Low Byte      |

| FE          | SPH                    | Stack Pointer High Byte     |

| FD          | RP                     | Register Pointer            |

| FC          | FLAGS                  | Program Control Flags       |

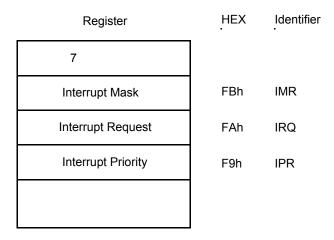

| FB          | IMR                    | Interrupt Mask Register     |

| FA          | IRQ                    | Interrupt Request Register  |

| F9          | IPR                    | Interrupt Priority Register |

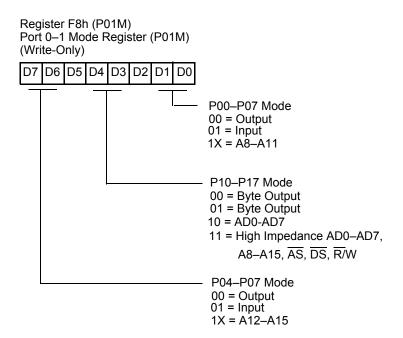

| F8          | P01M                   | Port 0–1 Mode Register      |

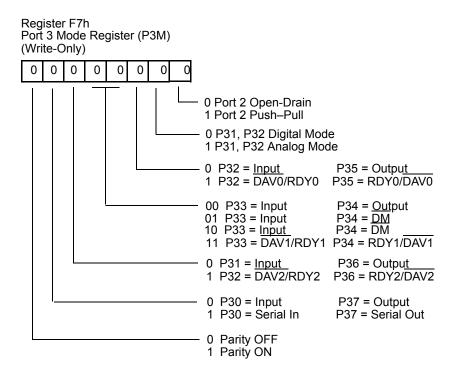

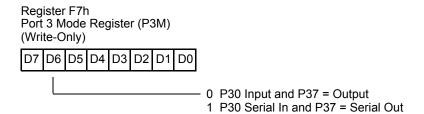

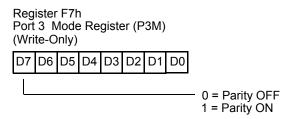

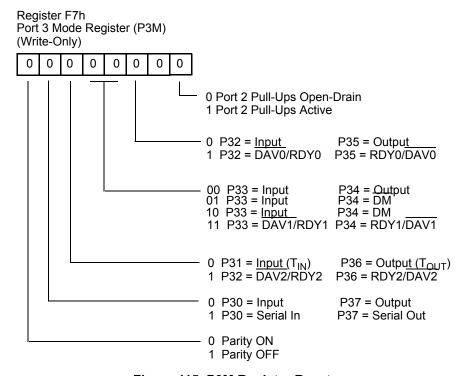

| F7          | P3M                    | Port 3 Mode Register        |

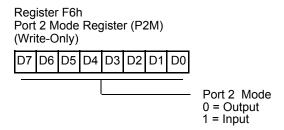

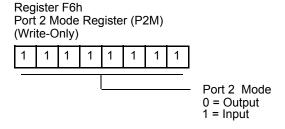

| F6          | P2M                    | Port 2 Mode Register        |

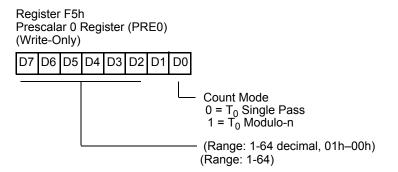

| F5          | PRE0                   | T0 Prescaler                |

**Table 2. Z8 Standard Register File (Continued)**

| Hex Address   | Register<br>Identifier | Register Description |

|---------------|------------------------|----------------------|

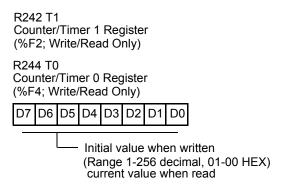

| F4            | T0                     | Timer/Counter 0      |

| F3            | PRE1                   | T1 Prescaler         |

| F2            | T1                     | Timer/Counter 1      |

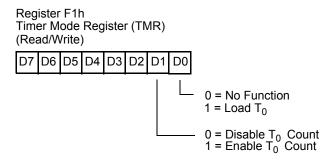

| F1            | TMR                    | Timer Mode           |

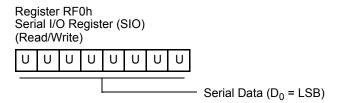

| F0            | SIO                    | Serial I/O           |

| EF            | R239                   |                      |

| General-Purpo | ose Registers (GPR)    |                      |

| 04            | R4                     |                      |

| 03            | P3                     | Port 3               |

| 02            | P2                     | Port 2               |

| 01            | P1                     | Port 1               |

| 00            | P0                     | Port 0               |

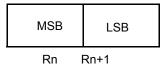

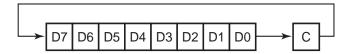

Registers can be accessed as either 8-bit or 16-bit registers using Direct, Indirect, or Indexed Addressing. All 236 general-purpose registers can be referenced or modified by any instruction that accesses an 8-bit register, without the requirement for special instructions. Registers accessed as 16 bits are treated as even-odd register pairs (there are 118 valid pairs). In this case, the data's most significant byte (MSB) is stored in the even numbered register, while the least significant byte (LSB) goes into the next higher odd numbered register. See Figure 2.

n = Even Address

Figure 2. 16-Bit Register Addressing

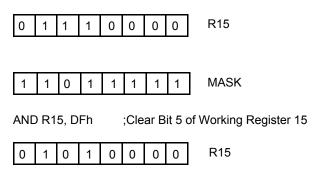

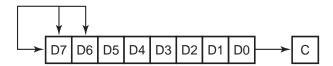

By using a logical instruction and a mask, individual bits within registers can be accessed for bit set, bit clear, bit complement, or bit test operations. For example, the instruction AND R15, MASK performs a bit clear operation, Figure 3 on page 7 displays this example.

Figure 3. Accessing Individual Bits (Example)

When instructions are executed, registers are read when defined as sources and written when defined as destinations. All General-Purpose Registers function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

### **General-Purpose Registers**

General-Purpose Registers are undefined after the device is powered up. The registers keep their last value after any reset, as long as the reset occurs in the  $V_{CC}$  voltage-specified operating range. It does not keep its last state from a  $V_{LV}$  reset if  $V_{CC}$  drops below 1.8 V.

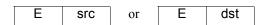

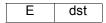

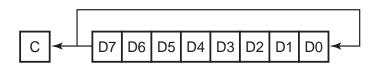

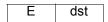

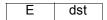

Note: Registers in Bank E0-EF may only be accessed through the working register and indirect addressing modes. Direct access cannot be used because the 4-bit working register address mode already uses the format [E | dst], where dst represents the working register number from 0h to Fh.

#### **RAM Protect**

The upper portion of the register file address space 80h to EFh (excluding the control registers) may be protected from reading and writing. The RAM Protect bit option is mask-programmable and is selected by the customer when the ROM code is submitted. After the mask option is selected, activate this feature from the internal ROM code to turn OFF/on the RAM Protect by loading either a 0 or 1 into the IMR register, bit D6. A 1 in D6 enables RAM Protect. Only devices that use registers 80h to EFh offer this feature.

# **Working Register Groups**

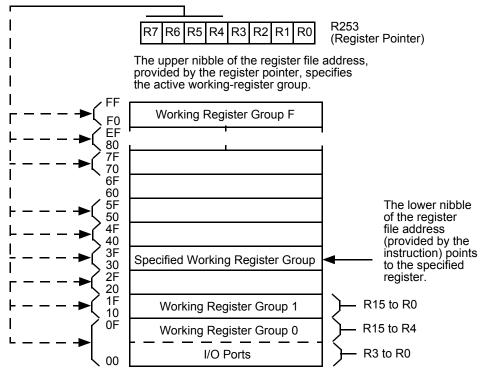

Z8<sup>®</sup> instructions can access 8-bit registers and register pairs (16-bit words) using either 4-bit or 8-bit address fields. 8-bit address fields refer to the actual address of the register. For example, Register 58h is accessed by calling upon its 8-bit binary equivalent, 01011000 (58h).

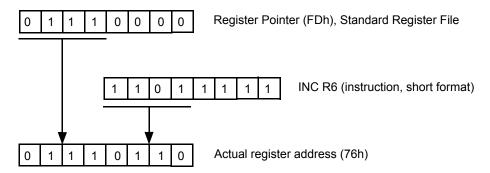

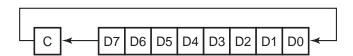

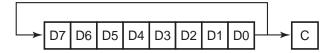

With 4-bit addressing, the register file is logically divided into 16 Working Register Groups of 16 registers each, as listed in Table 3. These 16 registers are known as Working Registers. A Register Pointer (one of the control registers, FDh) contains the base address of the active Working Register Group. The high nibble of the Register Pointer determines the current Working Register Group.

When accessing one of the Working Registers, the 4-bit address of the Working Register is combined within the upper four bits (high nibble) of the Register Pointer, thus forming the 8-bit actual address. Figure 4 on page 9 displays this operation. Because working registers are typically specified by short format instructions, there are fewer bytes of code required, which reduces execution time. In addition, when processing interrupts or changing tasks, the Register Pointer speeds context switching. A special Set Register Pointer (SRP) instruction sets the contents of the Register Pointer.

**Table 3. Working Register Groups**

| Register Pointer<br>(FDh) High Nibble | Working Register<br>Group (Hex) | Actual Registers<br>(Hex) |

|---------------------------------------|---------------------------------|---------------------------|

| 1111b                                 | F                               | F0-FF                     |

| 1110b                                 | E                               | E0-EF                     |

| 1101b                                 | D                               | D0-DF                     |

| 1100b                                 | С                               | C0-CF                     |

| 1011b                                 | В                               | B0-BF                     |

| 1010b                                 | Α                               | A0–AF                     |

| 1001b                                 | 9                               | 90–9F                     |

| 1000b                                 | 8                               | 80–8F                     |

| 0111b                                 | 7                               | 70–7F                     |

| 0110b                                 | 6                               | 60–6F                     |

| 0101b                                 | 5                               | 50–5F                     |

| 0100b                                 | 4                               | 40–4F                     |

| 0011b                                 | 3                               | 30–3F                     |

| 0010b                                 | 2                               | 20–2F                     |

| 0001b                                 | 1                               | 10–1F                     |

| 0000b                                 | 0                               | 00-0F                     |

Figure 4. Working Register Addressing Examples

\*Note: The full register file is shown. Refer to the selected device product specification for actual file size.

Figure 5. Register Pointer

#### **Error Conditions**

Registers in the Z8<sup>®</sup> Standard Register File must be correctly used because certain conditions produce inconsistent results and should be avoided.

- Registers F3h and F5h–F9h are write-only registers. If an attempt is made to read these registers, FFh is returned. Reading any write-only register returns FFh.

- When register FDh (Register Pointer) is read, the least significant four bits (lower nibble) indicate the current Expanded Register File Bank. (For example, 0000 indicates the Standard Register File, while 1010 indicates Expanded Register File Bank A.)

- When Ports 0 and 1 are defined as address outputs, registers 00h and 01h return 1s in each address bit location when reading.

- Writing to bits that are defined as timer output, serial output, or handshake output has no effect.

- The Z8 CPU instruction DJNZ uses any general-purpose working register as a counter.

- Logical instructions such as OR and AND require that the current contents of the operand be read. They therefore do not function properly on write-only registers.

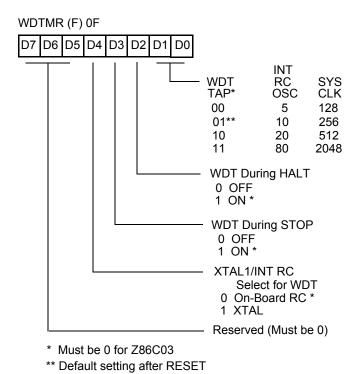

- The WDTMR register must be written within the first 60 internal system clocks (SCLK) of operation after a reset.

# **Z8 Expanded Register File**

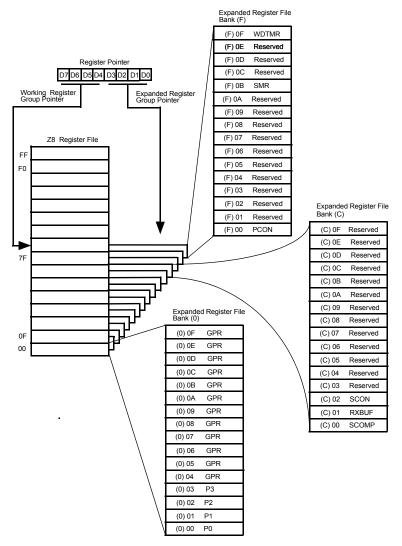

The standard register file of the Z8 CPU has been expanded to form 16 Expanded Register File (ERF) Banks, as displayed in Figure 6 on page 11. Each ERF Bank consists of up to 256 registers (the same amount as in the Standard Register File) that can then be divided into 16 Working Register Groups. This expansion allows for access to additional feature/peripheral control and data registers.

\*Note: The fully implemented register file is shown. Refer to the specific product specification for actual register file architecture implemented.

Figure 6. Expanded Register File Architecture

Currently, three out of the possible sixteen Z8 ERF Banks have been implemented. ERF Bank 0, also known as the Z8<sup>®</sup> Standard Register File, has all 256 bytes defined, as displayed in Figure 7 on page 12. Only Working Register Group 0 (register addresses 00h to 0Fh) has been defined for ERF Bank C and ERF Bank F (see Table 4 on page 12). All other working register groups in ERF Banks C and F, as well as the remaining thirteen ERF Banks, are not implemented. All are reserved for future use.

When an ERF Bank is selected, register addresses 00h to 0Fh access those sixteen ERF Bank registers—in effect replacing the first sixteen locations of the Z8<sup>®</sup> Standard Register File.

For example, if ERF Bank C is selected, the Z8 Standard Registers 00h through 0Fh are no longer accessible. Registers 00h through 0Fh are now the 16 registers from ERF Bank C, Working Register Group 0. No other Z8 Standard Registers are affected because only Working Register Group 0 is implemented in ERF Bank C.

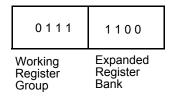

Access to the ERF is accomplished through the Register Pointer (FDh). The lower nibble of the Register Pointer determines the ERF Bank while the upper nibble determines the Working Register Group within the register file, as displayed in Figure 7.

Select ERF Bank Ch Working Register Group 7h

Figure 7. Register Pointer Example

The value of the lower nibble in the Register Pointer (FDh) corresponds to the ERF Bank identification. Table 4 lists the lower nibble value and the register file assigned to it.

**Table 4. ERF Bank Address**

| -                                 |     |                               |

|-----------------------------------|-----|-------------------------------|

| Register Pointer (FDh) Low Nibble | Hex | Register File                 |

| 0000b                             | 0   | Z8 Standard Register File*    |

| 0001b                             | 1   | Expanded Register File Bank 1 |

| 0010b                             | 2   | Expanded Register File Bank 2 |

| 0011b                             | 3   | Expanded Register File Bank 3 |

| 0100b                             | 4   | Expanded Register File Bank 4 |

| 0101b                             | 5   | Expanded Register File Bank 5 |

| 0110b                             | 6   | Expanded Register File Bank 6 |

| 0111b                             | 7   | Expanded Register File Bank 7 |

| 1000b                             | 8   | Expanded Register File Bank 8 |

Table 4. ERF Bank Address (Continued)

| Pagistar Painter                                                                             |     |                               |  |  |  |

|----------------------------------------------------------------------------------------------|-----|-------------------------------|--|--|--|

| Register Pointer (FDh) Low Nibble                                                            | Hex | Register File                 |  |  |  |

| 1001b                                                                                        | 9   | Expanded Register File Bank 9 |  |  |  |

| 1010b                                                                                        | Α   | Expanded Register File Bank A |  |  |  |

| 1011b                                                                                        | В   | Expanded Register File Bank B |  |  |  |

| 1100b                                                                                        | С   | Expanded Register File Bank C |  |  |  |

| 1101b                                                                                        | D   | Expanded Register File Bank D |  |  |  |

| 1110b                                                                                        | Е   | Expanded Register File Bank E |  |  |  |

| 1111b                                                                                        | F   | Expanded Register File Bank F |  |  |  |

| *The $Z8^{\circledR}$ Standard Register File is equivalent to Expanded Register File Bank 0. |     |                               |  |  |  |

The upper nibble of the register pointer selects which group of 16 bytes in the Register File, out of the 256 total bytes, is accessed as working registers. Table 5 lists an example.

**Table 5. Register Pointer Access Example**

| R253 RP = 00h    | ;ERF Bank 0, Working Reg.<br>Group 0 |

|------------------|--------------------------------------|

|                  | R0 = Port 0 = 00h                    |

|                  | R1 = Port 1 = 01h                    |

|                  | R2 = Port 2 = 02h                    |

|                  | R3 = Port 3 = 03h                    |

|                  | R11 = GPR OBh                        |

|                  | R15 = GPR 0Fh                        |

| If R253 RP = 0Fh | ;ERF Bank F, Working Reg.<br>Group 0 |

|                  | R0 = PCON = 00h                      |

|                  | R1 = Reserved = 01h                  |

|                  | R2 = Reserved = 02h                  |

|                  | R11 = SMR = 0Bh                      |

|                  | R15 = WDTMR = 0Fh                    |

**Table 5. Register Pointer Access Example (Continued)**

| If R253 RP = FFh |                         |                |

|------------------|-------------------------|----------------|

|                  | ;ERF Bank F<br>Group F. | , Working Reg. |

|                  | 00h = PCON              |                |

|                  | R0 = SIO                | 01h = Reserved |

|                  | R1 = TMR                | 02h = Reserved |

|                  |                         |                |

|                  | R2 = T1                 | OBh = SMR      |

|                  |                         |                |

|                  | R15 = SPL               | OFh = WDTMR    |

Because enabling an ERF Bank (C or F) only changes register addresses 00h to 0Fh, the working register pointer can be used to access either the selected ERF Bank (Bank C or F, Working Register Group 0) or the Z8<sup>®</sup> Standard Register File (ERF Bank 0, Working Register Groups 1 through F).

When an ERF Bank other than Bank 0 is enabled, the first 16 bytes of the Z8 Standard Register File (I/O ports 0 to 3, Groups 4 to F) are no longer accessible (the selected ERF Bank, Registers 00h to 0Fh are accessed instead). It is important to re-initialize the Register Pointer to enable ERF Bank 0 when these registers are required for use.

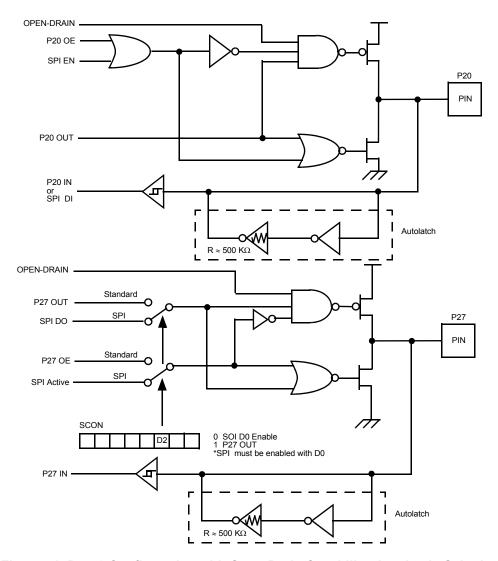

The SPI register is mapped into ERF Bank C. Access is easily done using the example in Table 6.

Table 6. ERF Bank C Access Example

| LD | RP, #0Ch | ;Select ERF Bank C working      |

|----|----------|---------------------------------|

|    |          | ;register group 0 for access.   |

| LD | R2,#xx   | ;access SCON                    |

| LD | R1, #xx  | ;access RXBUF                   |

| LD | RP, #00h | ;Select ERF Bank 0 so I/O ports |

|    |          | ;are again accessible.          |

**Table 7. Z8 ERF Bank Layout**

| ERF Bank | ERF                                                                                                        |

|----------|------------------------------------------------------------------------------------------------------------|

| Fh       | PCON, SMR, WDT, (00h, 0Bh, 0Fh), Working Register Group 0 only implemented.                                |

| Eh       | Not implemented (reserved)                                                                                 |

| Dh       | Not implemented (reserved)                                                                                 |

| Ch       | SPI Registers: SCOMP, RXBUF, SCON (00h, 01h, 02h), Working Register Group 0 only implemented.              |

| Bh       | Not implemented (reserved)                                                                                 |

| Ah       | Not implemented (reserved)                                                                                 |

| 9h       | Not implemented (reserved)                                                                                 |

| 8h       | Not implemented (reserved)                                                                                 |

| 7h       | Not implemented (reserved)                                                                                 |

| 6h       | Not implemented (reserved)                                                                                 |

| 5h       | Not implemented (reserved)                                                                                 |

| 4h       | Not implemented (reserved)                                                                                 |

| 3h       | Not implemented (reserved)                                                                                 |

| 2h       | Not implemented (reserved)                                                                                 |

| 1h       | Not implemented (reserved)                                                                                 |

| 0h       | Z8 Ports 0, 1, 2, 3, and General-Purpose Registers $04h$ to $EFh$ , and control registers $F0h$ to $FFh$ . |

Refer to the specific product specification to determine the above registers are implemented.

# Z8<sup>®</sup> Control and Peripheral Registers

# Standard Z8 Registers

The standard Z8 control registers govern the operation of the CPU. Any instruction which references the register file can access these control registers. The following control registers are available:

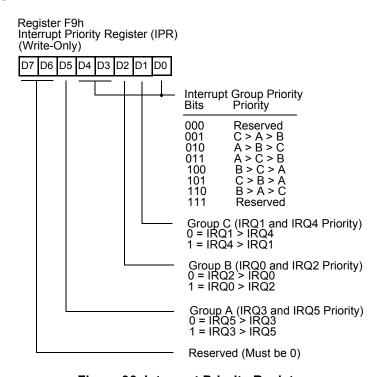

- Interrupt Priority Register (IPR)

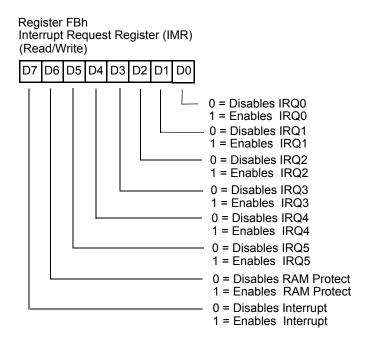

- Interrupt Mask Register (IMR)

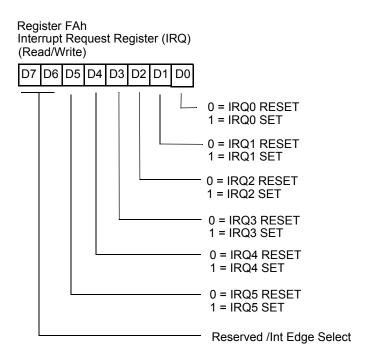

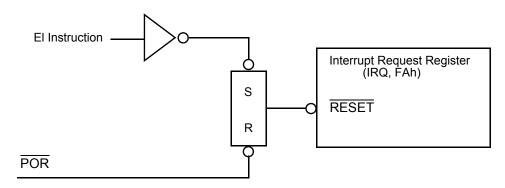

- Interrupt Request Register (IRQ)

- Program Control Flags (FLAGS)

- Register Pointer (RP)

- Stack Pointer High-Byte (SPH)

- Stack Pointer Low-Byte (SPL)

The Z8<sup>®</sup> CPU uses a 16-bit Program Counter (PC) to determine the sequence of current program instructions. The PC is not an addressable register.

Peripheral registers are used to transfer data, configure the operating mode, and control the operation of the on-chip peripherals. Any instruction that references the register file can access the peripheral registers. The peripheral registers are:

- Serial I/O (SIO)

- Timer Mode (TMR)

- Timer/Counter 0 (T0)

- T0 Prescaler (PRE0)

- Timer/Counter 1 (T1)

- T1 Prescaler (PRE1)

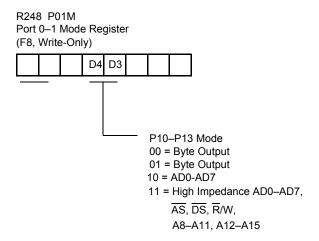

- Port 0–1 Mode (P01M)

- Port 2 Mode (P2M)

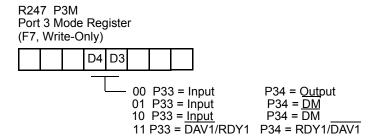

- Port 3 Mode (P3M)

In addition, the four port registers (P0–P3) are considered to be peripheral registers.

# **Expanded Z8 Registers**

The expanded Z8 control registers govern the operation of additional features or peripherals. Any instruction which references the register file can access these registers.

The ERF contains the control registers for WDT, Port Control, Serial Peripheral Interface (SPI), and the SMR functions. Figure 6 on page 11 displays the layout of the Register Banks in the ERF. Register Bank C in the ERF consists of the registers for the SPI. Table 8 lists the registers within ERF Bank C, Working Register Group 0.

Table 8. ERF Bank C WR Group 0

| Register | Function | Working Register |

|----------|----------|------------------|

| F        | Reserved | R15              |

| E        | Reserved | R14              |

| D        | Reserved | R13              |

Table 8. ERF Bank C WR Group 0 (Continued)

| Register | Function                  | Working Register |

|----------|---------------------------|------------------|

| С        | Reserved                  | R12              |

| В        | Reserved                  | R11              |

| A        | Reserved                  | R10              |

| 9        | Reserved                  | R9               |

| 8        | Reserved                  | R8               |

| 7        | Reserved                  | R7               |

| 6        | Reserved                  | R6               |

| 5        | Reserved                  | R5               |

| 4        | Reserved                  | R4               |

| 3        | Reserved                  | R3               |

| 2        | SPI Control (SCON)        | R2               |

| 1        | SPI Tx/Rx Data (Roxburgh) | R1               |

| 0        | SPI Compare (SCOMP)       | R0               |

|          |                           |                  |

Working Register Group 0 in ERF Bank 0 consists of the registers for Z8<sup>®</sup> General-Purpose Registers and ports. Table 9 lists the registers within this group.

Table 9. ERF Bank 0 WR Group 0

| Register | Function                 | Working Register |

|----------|--------------------------|------------------|

| F        | General-Purpose Register | R15              |

| E        | General-Purpose Register | R14              |

| D        | General-Purpose Register | R13              |

| С        | General-Purpose Register | R12              |

| В        | General-Purpose Register | R11              |

| A        | General-Purpose Register | R10              |

| 9        | General-Purpose Register | R9               |

| 8        | General-Purpose Register | R8               |

| 7        | General-Purpose Register | R7               |

| 6        | General-Purpose Register | R6               |

| 5        | General-Purpose Register | R5               |

Table 9. ERF Bank 0 WR Group 0 (Continued)

| Register | Function                 | Working Register |

|----------|--------------------------|------------------|

| 4        | General-Purpose Register | R4               |

| 3        | Port 3                   | R3               |

| 2        | Port 2                   | R2               |

| 1        | Port 1                   | R1               |

| 0        | Port 0                   | R0               |

Working Register Group 0 in ERF Bank F consists of the control registers for STOP mode, WDT, and port control. Table 10 lists the registers within this group.

Table 10. ERF Bank F WR Group 0

| Register | Function | Working Register |

|----------|----------|------------------|

| F        | WDTMR    | R15              |

| E        | Reserved | R14              |

| D        | Reserved | R13              |

| С        | Reserved | R12              |

| В        | SMR      | R11              |

| A        | Reserved | R10              |

| 9        | Reserved | R9               |

| 8        | Reserved | R8               |

| 7        | Reserved | R7               |

| 6        | Reserved | R6               |

| 5        | Reserved | R5               |

| 4        | Reserved | R4               |

| 3        | Reserved | R3               |

| 2        | Reserved | R2               |

| 1        | Reserved | R1               |

| 0        | PCON     | R0               |

# **Program Memory**

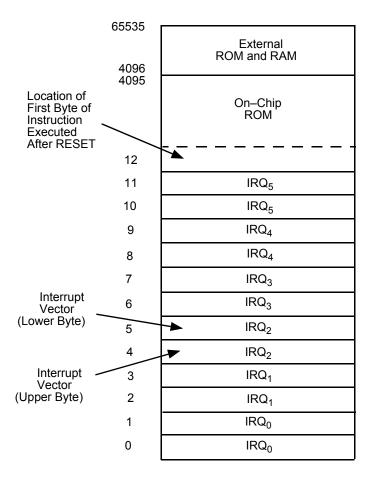

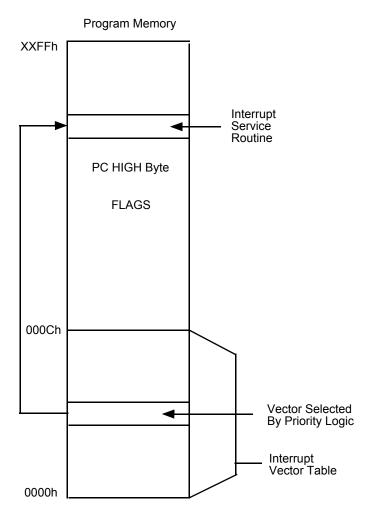

The first 12 bytes of Program Memory are reserved for the interrupt vectors, as displayed in Figure 8 on page 20. These locations contain six 16-bit vectors that correspond to the six available interrupts. Address 12 up to the maximum ROM address consists of on-chip mask-programmable ROM. Refer to the product data sheet for the exact program, data, register memory size, and address range available. At addresses outside the internal ROM, the Z8<sup>®</sup> CPU executes external Program Memory fetches through Port 0 and Port 1 in Address/Data mode for devices with Port 0 and Port 1 featured. Otherwise, the program counter continues to execute NOPs up to address FFFFh, roll over to 0000h, and continue to fetch executable code (see Figure 8).

The internal Program Memory is one-time programmable (OTP) or mask programmable dependent on the specific device. A ROM protect feature prevents dumping of the ROM contents by inhibiting execution of the LDC, LDCI, LDE, and LDEI instructions to Program Memory in all modes. ROM look-up tables cannot be used with this feature.

The ROM Protect option is mask-programmable, to be selected when the ROM code is submitted. For the OTP ROM, the ROM Protect option is an OTP programming option.

Figure 8. Z8<sup>®</sup> Program Memory Map

# **Z8<sup>®</sup> External Memory**

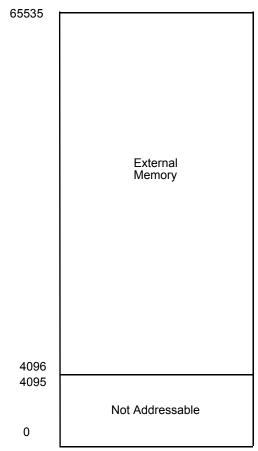

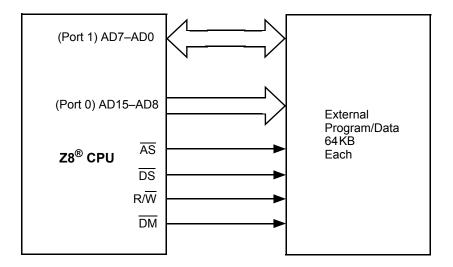

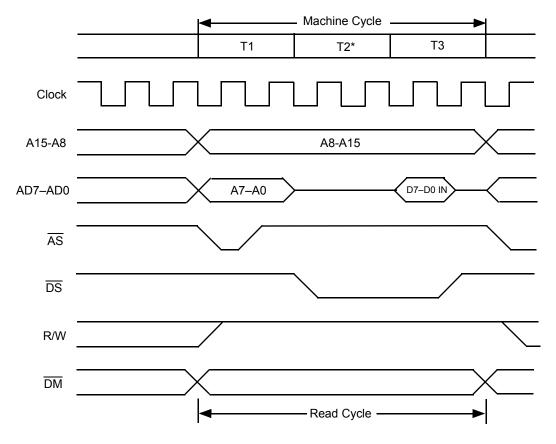

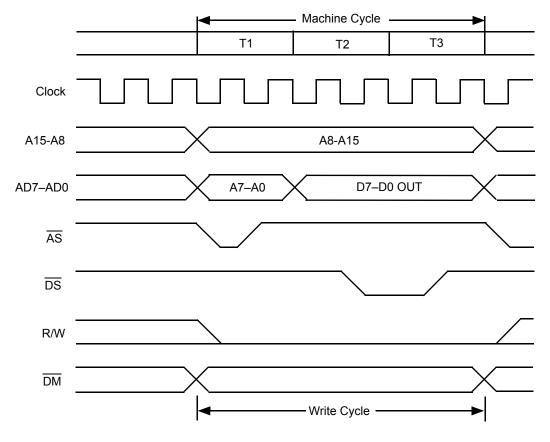

Z8 CPU, in some cases, has the capability to access external Program Memory with the 16-bit Program Counter. To access external Program Memory the Z8 CPU offers multiplexed address/data lines (AD7–AD0) on Port 1 and address lines (A15–A8) on Port 0. This feature only applies to devices that offer Port 0 and Port 1. The maximum external address is FFFF. This memory interface is supported by the control lines  $\overline{\rm AS}$  (Address Strobe),  $\overline{\rm DS}$  (Data Strobe), and R/W (Read/Write). The origin of the external Program Memory starts after the last address of the internal ROM. Figure 9 on page 21 displays an example of external Program Memory for the Z8 CPU.

### **External Data Memory**

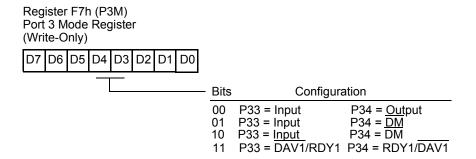

The Z8 CPU, in some cases, can address <u>up</u> to 60 KB of external data memory beginning at location 4096. External data memory ( $\overline{DM}$ ) can be included with, or separated from, the external Program Memory space.  $\overline{DM}$ , an optional I/O function that can be programmed to appear on pin P34, is used to distinguish between data and Program Memory space. The state of the  $\overline{DM}$  signal is controlled by the type of instruction being executed. An LDC opcode references Program Memory ( $\overline{DM}$  inactive), and an LDE instruction references data memory ( $\overline{DM}$  active Low). You must configure Port 3 Mode Register (P3M) bits D3 and D4 for this mode.

\*Note: For additional information on using external memory, see Chapter 10 of this manual. For exact memory addressing options available, see the device product specification.

Figure 9. External Memory Map

# Z8<sup>®</sup> Stacks

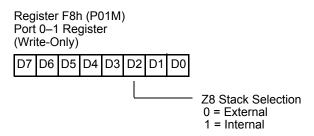

Stack operations can occur in either the Z8 Standard Register File or external data memory. Under software control, Port 0–1 Mode register (F8h) selects the stack location. Only the General-Purpose Registers can be used for the stack when the internal stack is selected.

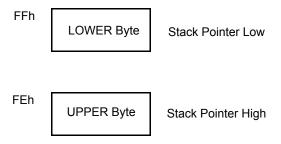

The register pair FEh and FFh form the 16-bit Stack Pointer (SP), that is used for all stack operations. The stack address is stored with the MSB in FEh and LSB in FFh, see Figure 10.

Figure 10. Stack Pointer

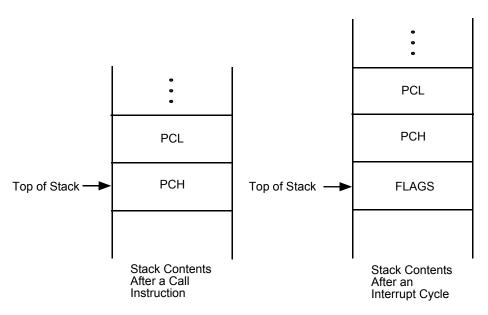

The stack address is decremented prior to a PUSH operation and incremented after a POP operation. The stack address always points to the data stored on the top of the stack. The Z8 CPU stack is a return stack for CALL instructions and interrupts, as well as a data stack.

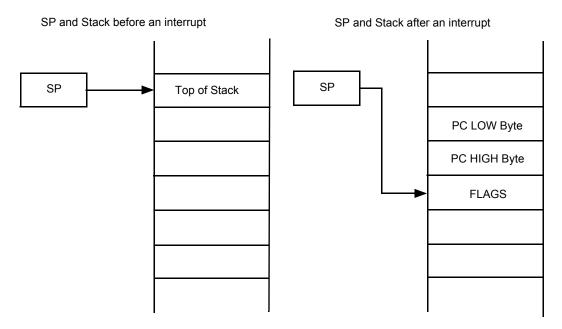

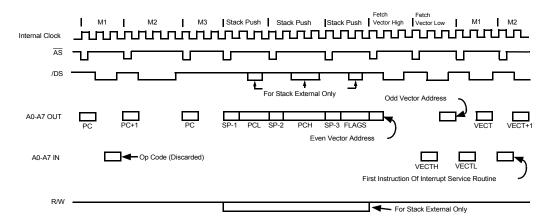

During a CALL instruction, the contents of the PC are saved on the stack. The PC is restored during a RETURN instruction. Interrupts cause the contents of the PC and Flag registers to be saved on the stack. The IRET instruction restores them (see Figure 11 on page 23).

When the Z8 CPU is configured for an internal stack (using the Z8 Standard Register File), register FFh serves as the Stack Pointer. The value in FEh is ignored. FEh can be used as a general-purpose register in this case only.

An overflow or underflow can occur when the stack address is incremented or decremented during normal stack operations. The programmer must prevent this occurrence, or unpredictable operation happens.

Figure 11. Stack Operations

# Clock

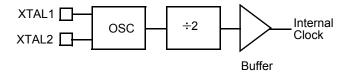

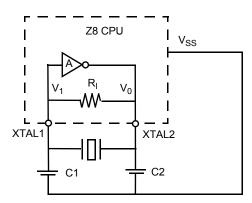

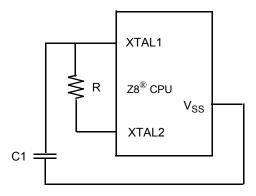

Z8<sup>®</sup> CPU derives its timing from on-board clock circuitry connected to pins XTAL1 and XTAL2. The clock circuitry consists of an oscillator, a divide-by-two shaping circuit, and a clock buffer. Figure 12 displays the clock circuitry. The oscillator's input is XTAL1 and its output is XTAL2. The clock can be driven by a crystal, a ceramic resonator, LC clock, RC, or an external clock source.

#### Frequency Control

In some cases, the Z8 CPU has an EPROM/OTP option or a Mask ROM option bit to bypass the divide-by-two flip flop in Figure 12. This feature is used in conjunction with the low EMI option. When low EMI is selected, the device output drive and oscillator drive is reduced to approximately 25 percent of the standard drive and the divide-by-two flip flop is bypassed such that the XTAL clock frequency is equal to the internal system clock frequency. In this mode, the maximum frequency of the XTAL clock is 4 MHz. Refer to specific product specification for availability of options and output drive characteristics.

Figure 12. Z8<sup>®</sup> CPU Clock Circuit

#### **Clock Control**

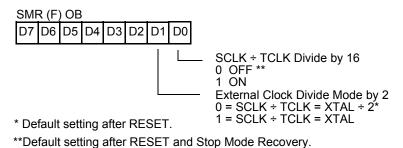

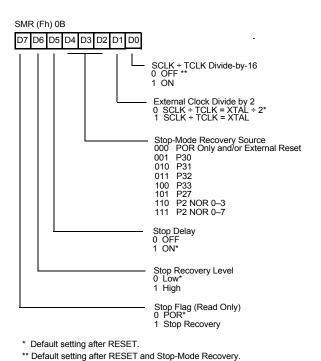

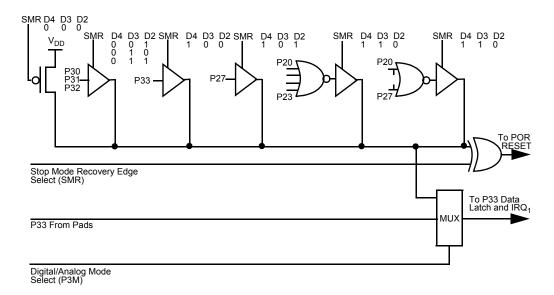

In some cases, the Z8 CPU offers software control of the internal system clock via programming register bits. The bits are located in the Stop Mode Recovery Register in Expanded Register File Bank F, Register OBh. This register selects the clock divide value and determines the mode of Stop Mode Recovery (see Figure 13 on page 25). Refer to the specific product specification for availability of this feature/register.

Figure 13. Stop Mode Recovery Register (Write-Only Except D7, Which is Read-Only)

## SCLK + TCLK Divide-By-16 Select

The D0 bit of the SMR controls a divide-by-16 prescaler of SCLK ÷ TCLK. The purpose of this control is to selectively reduce device power consumption during normal processor execution (SCLK control) and/or HALT mode (where TCLK sources counter/timers and interrupt logic).

### **External Clock Divide-By-Two**

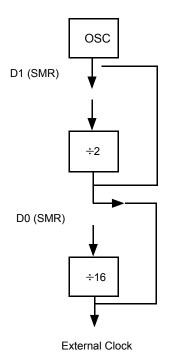

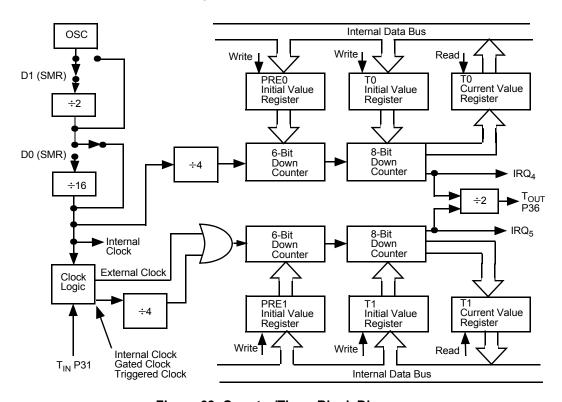

The D1 bit can eliminate the oscillator divide-by-two circuitry. When this bit is 0, SCLK (System Clock) and TCLK (Timer Clock) are equal to the external clock frequency divided by two. The SCLK  $\div$  TCLK is equal to the external clock frequency when this bit is set (D1 = 1). Using this bit, together with D7 of PCON, further helps lower EMI (D7 (PCON) = 0, D1 (SMR) = 1). The default setting is 0. Maximum frequency is 4 MHz with D1 = 1 (see Figure 14 on page 26).

Figure 14. External Clock Circuit

## **Oscillator Control**

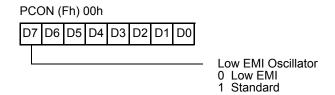

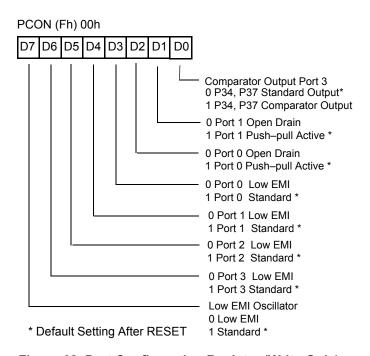

In some cases, the Z8<sup>®</sup> CPU offers software control of the oscillator to select low EMI drive or standard drive. The selection is done by programming bit D7 of the Port Configuration (PCON) register (see Figure 15 on page 26). The PCON register is located in Expanded Register File Bank F, Register 00h.

A 1 in bit D7 configures the oscillator with standard drive, while a 0 configures the oscillator with Low EMI drive. This only affects the drive capability of the oscillator and does not affect the relationship of the XTAL clock frequency to the internal system clock (SCLK).

Figure 15. Port Configuration Register (Write-Only)

27

# **Oscillator Operation**

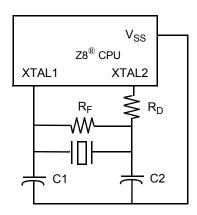

The Z8 $^{\circledR}$  CPU uses a Pierce oscillator with an internal feedback (see Figure 16). The advantages of this circuit are low cost, large output signal, low-power level in the crystal, stability with respect to  $V_{CC}$  and temperature, and low impedances (not disturbed by stray affects).

One drawback is the requirement for high gain in the amplifier to compensate for feedback path losses. The oscillator amplifies its own noise at start-up until it settles at the frequency that satisfies the gain/phase requirements  $A \times B = 1$ , where  $A = V_0/V_1$  is the gain of the amplifier and  $B = V_1/V_0$  is the gain of the feedback element. The total phase shift around the loop is forced to zero (360 degrees). Because VIN must be in phase with itself, the amplifier/inverter provides 180 degree phase shift and the feedback element is forced to provide the other 180 degrees of phase shift.

R1 is a resistive component placed from output to input of the amplifier. The purpose of this feedback is to bias the amplifier in its linear region and to provide the start-up transition.

Capacitor  $C_2$  combined with the amplifier output resistance provides a small phase shift. It also provides some attenuation of overtones.

Capacitor C<sub>1</sub> combined with the crystal resistance provides additional phase shift.

$C_1$  and  $C_2$  can affect the start-up time if they increase dramatically in size. As  $C_1$  and  $C_2$  increase, the start-up time increases until the oscillator reaches a point where it does not start up any more.

For fast and reliable oscillator start-up over the manufacturing process range, Zilog<sup>®</sup> recommends that the load capacitors be sized as low as possible without resulting in overtone operation.

Figure 16. Pierce Oscillator with Internal Feedback Circuit

# Layout

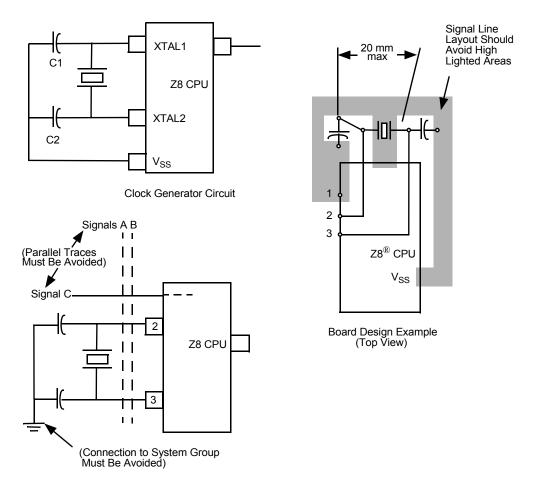

Traces connecting crystal, caps, and the  $Z8^{\mathbb{R}}$  CPU oscillator pins should be as short and wide as possible. This reduces parasitic inductance and resistance. The components (caps, crystal, resistors) should be placed as close as possible to the oscillator pins of the Z8 CPU.

The traces from the oscillator pins of the IC and the ground side of the lead caps should be guarded from all other traces (clock,  $V_{CC}$ , address/data lines, system ground) to reduce cross talk and noise injection. This is usually accomplished by keeping other traces and system ground trace planes away from the oscillator circuit and by placing a Z8 CPU device  $V_{SS}$  ground ring around the traces/components. The ground side of the oscillator lead caps should be connected to a single trace to the Z8 CPU's  $V_{SS}$  (GND) pin. It should not be shared with any other system ground trace or components except at the Z8 CPU's  $V_{SS}$  pin. This is to prevent differential system ground noise injection into the oscillator (see Figure 17 on page 29).

## Indications of an Unreliable Design

Start-up time and output level are two major indicators that are used in working designs to determine their reliability over full lot and temperature variations. These two indicators are described below.

**Start-Up Time**—If start-up time is excessive, or varies widely from unit to unit, there is probably a gain problem. C1/C2 must be reduced; the amplifier gain is not adequate at frequency, or crystal resistance is too large.

**Output Level—**The signal at the amplifier output should swing from ground to  $V_{CC}$ . This indicates there is adequate gain in the amplifier. As the oscillator starts up, the signal amplitude grows until clipping occurs, at which point the loop gain is effectively reduced to unity and constant oscillation is achieved. A signal of less than 2.5 V peak-to-peak is an indication that low gain may be a problem. Either  $C_1$  or  $C_2$  should be made smaller or a low-resistance crystal should be used.

# **Circuit Board Design Rules**

The following circuit board design rules are suggested:

- To prevent induced noise the crystal and load capacitors should be physically located as close to the Z8 CPU as possible.

- Signal lines should not run parallel to the clock oscillator inputs. In particular, the

crystal input circuitry and the internal system clock output should be separated as

much as possible.

- V<sub>CC</sub> power lines should be separated from the clock oscillator input circuitry.

- Resistivity between XTAL1 or XTAL2 and the other pins should be greater than 10  $M\Omega$

Figure 17. Circuit Board Design Rules

# **Crystals and Resonators**

Crystals and ceramic resonators, displayed in Figure 18 should have the characteristics listed in Table 11 to ensure proper oscillator operation.

Table 11. Crystal/Resonator Characteristics

| Crystal Cut         | AT (crystal only)               |

|---------------------|---------------------------------|

| Mode                | Parallel, Fundamental mode      |

| Crystal Capacitance | <7pF                            |

| Load Capacitance    | 10 pF < CL < 220 pF, 15 typical |

| Resistance          | 100Ω max                        |

Depending on operation frequency, the oscillator may require the addition of capacitors C1 and C2 (displayed in Figure 18). The capacitance values are dependent on the manufacturer's crystal specifications.

Figure 18. Crystal/Ceramic Resonator Oscillator

Figure 19. LC Clock

In most cases, the  $R_D$  is  $0\Omega$  and  $R_F$  is infinite. It is determined and specified by the crystal/ceramic resonator manufacturer. The  $R_D$  can be increased to decrease the amount of drive from the oscillator output to the crystal. It can also be used as an adjustment to avoid clipping of the oscillator signal to reduce noise. The  $R_F$  can be used to improve the start-up of the crystal/ceramic resonator. The  $Z8^{\circledR}$  oscillator already has an internal shunt resistor in parallel to the crystal/ceramic resonator.

UM001604-0108 Clock

Figure 20. External Clock

In Figure 18 through Figure 20,  $Zilog^{\circledR}$  recommends that you connect the load capacitor ground trace directly to the  $V_{SS}$  (GND) pin of the  $Z8^{\circledR}$  CPU to ensure that no system noise is injected into the Z8 clock. This trace should not be shared with any other components except at the  $V_{SS}$  pin of the Z8 CPU.

In some cases, the Z8 CPU's XTAL1 pin also functions as one of the EPROM high-voltage mode programming pins or as a special factory test pin. In this case, applying 2 V above  $V_{CC}$  on the XTAL1 pin causes the device to enter one of these modes. Because this pin accepts high voltages to enter these respective modes, the standard input protection diode to  $V_{CC}$  is not on XTAL1. Zilog recommends that in applications where the Z8 CPU is exposed to much system noise, a diode from XTAL1 to  $V_{CC}$  be used to prevent accidental enabling of these modes. This diode does not affect the crystal/ceramic resonator operation.

**Note:** A parallel resonant crystal or resonator data sheet specifies a load capacitor value that is the series combination of  $C_1$  and  $C_2$ , including all parasitics (PCB and holder).

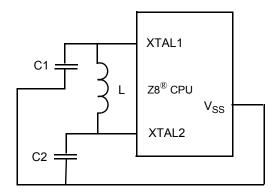

# **LC Oscillator**

The Z8 CPU oscillator can use a LC network to generate a XTAL clock (see Figure 19 on page 30).

The frequency stays stable over  $V_{CC}$  and temperature. The oscillation frequency is determined by following equation.

Frequency =

$$\frac{1}{2\pi(LC_T)^{1/2}}$$

where L is the total inductance including parasitics and  $C_T$  is the total series capacitance including the parasitics.

UM001604-0108 Clock

Simple series capacitance is calculated using the following equation:

$$\frac{1}{C_{T}} = \frac{1}{C_{1}} + \frac{1}{C_{2}}$$

If  $C_{1} = C_{2}$

$$\frac{1}{C_{T}} = \frac{2}{C_{1}}$$

$$C_{1} = 2C_{T}$$

Sample calculation for capacitance  $C_1$  and  $C_2$  of 5.83 MHz frequency and inductance value of 27  $\mu H$ .

$$5.83 (10^6) = \frac{1}{2\pi [2.7 (10^{-6}) C_T] 1/2}$$

$C_T = 27.6 \text{ pF}$

Therefore,  $C_1 = 55.2 \text{ pF}$  and  $C_2 = 55.2 \text{ pF}$ .

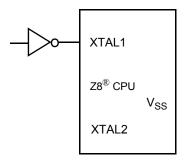

# **RC Oscillator**

In some cases, the Z8 $^{\circledR}$  CPU features an RC oscillator option. Refer to the specific product specification for availability. The RC oscillator requires a resistor across XTAL1 and XTAL2. An additional load capacitor is required from the XTAL1 input to  $V_{SS}$  pin, see Figure 21.

Figure 21. RC Clock

UM001604-0108 Clock

# Reset

This section describes the  $Z8^{\textcircled{R}}$  CPU reset conditions, reset timing, and register initialization procedures. Reset is generated by Power-On Reset (POR), Reset Pin, Watchdog Timer (WDT), and Stop Mode Recovery.

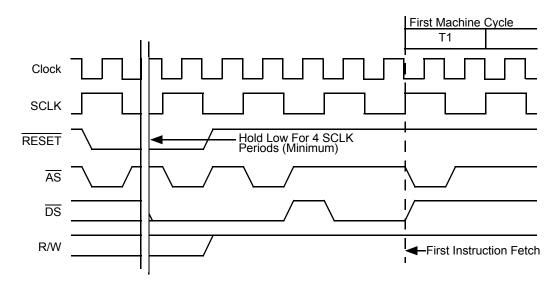

A system reset overrides all other operating conditions and puts the Z8 CPU into a known state. To initialize the chip's internal logic, the RESET input must be held Low for at least 21 SCP or 5 XTAL clock cycles. The control register and ports are reset to their default conditions after a POR, a reset from the RESET pin, or WDT time-out while in RUN mode and HALT mode. The control registers and ports are not reset to their default conditions after Stop Mode Recovery and WDT time-out while in STOP mode.

While  $\overline{RESET}$  pin is Low,  $\overline{AS}$  is output at the internal clock rate,  $\overline{DS}$  is forced Low, and  $R/\overline{W}$  remains High. The program counter is loaded with 000Ch. I/O ports and control registers are configured to their default reset state.

Resetting the Z8 CPU does not affect the contents of the general-purpose registers.

# **Reset Pin, Internal POR Operation**

In some cases, the Z8 CPU hardware RESET pin initializes the control and peripheral registers, as listed in Table 12 on page 34 through Table 15 on page 37. Specific reset values are shown by 1 or 0, while bits whose states are unknown are indicated by the letter U. Table 12 on page 34 through Table 15 on page 37 list the reset conditions for the Z8 CPU.

**Note:** The register file reset state is device dependent. Refer to the selected device product specifications for register availability and reset state.

| Register |                      |   |   |   | Ві | its |   |   |   |                                                      |

|----------|----------------------|---|---|---|----|-----|---|---|---|------------------------------------------------------|

| (Hex)    | Register Name        | 7 | 6 | 5 | 4  | 3   | 2 | 1 | 0 | Comments                                             |

| F0       | Serial I/O           | U | U | U | U  | U   | U | U | U |                                                      |

| F1       | Timer Mode           | 0 | 0 | 0 | 0  | 0   | 0 | 0 | 0 | Counter/Timers stopped.                              |

| F2       | Counter/Timer1       | U | U | U | U  | U   | U | U | U |                                                      |

| F3       | T1 Prescaler         | U | U | U | U  | U   | U | 0 | 0 | Single-pass count mode, external clock source.       |

| F4       | Counter/Timer0       | U | U | U | U  | U   | U | U | U |                                                      |

| F5       | T0 Prescaler         | U | U | U | U  | U   | U | U | 0 | Single-pass count mode.                              |

| F6       | Port 2 Mode          | 1 | 1 | 1 | 1  | 1   | 1 | 1 | 1 | All inputs.                                          |

| F7       | Port 3 Mode          | 0 | 0 | 0 | 0  | 0   | 0 | 0 | 0 | Port 2 open-drain, P33–P30<br>Input, P37–P34 Output. |

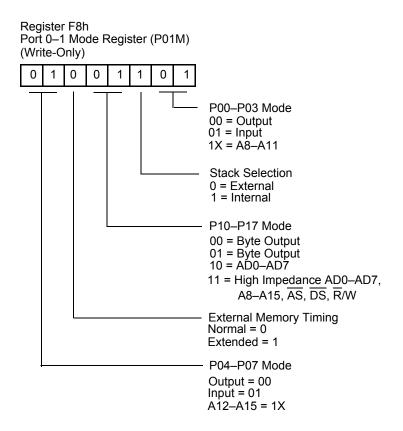

| F8       | Port 0–1 Mode        | 0 | 1 | 0 | 0  | 1   | 1 | 0 | 1 | Internal Stack, Normal Memory Timing.                |

| F9       | Interrupt Priority   | U | U | U | U  | U   | U | U | U |                                                      |

| FA       | Interrupt Request    | 0 | 0 | 0 | 0  | 0   | 0 | 0 | 0 | All Interrupts Cleared.                              |

| FB       | Interrupt Mask       | 0 | U | U | U  | U   | U | U | U | Interrupts Disabled.                                 |

| FC       | Flags                | U | U | U | U  | U   | U | U | U |                                                      |

| FD       | Register Pointer     | 0 | 0 | 0 | 0  | 0   | 0 | 0 | 0 |                                                      |

| FE       | Stack Pointer (High) | U | U | U | U  | U   | U | U | U |                                                      |

| FF       | Stack Pointer (Low)  | U | U | U | U  | U   | U | U | U |                                                      |

Program execution starts 5 to 10 clock cycles after internal RESET has returned High. The initial instruction fetch is from location 000Ch. Figure 22 on page 35 displays reset timing.

Figure 22. Reset Timing

After a reset, the first routine executed should be one that initializes the control registers to the required system configuration.

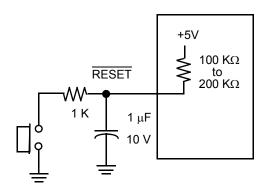

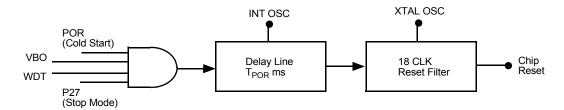

The  $\overline{RESET}$  pin is the input of a Schmitt-Triggered circuit. Resetting the  $Z8^{\circledR}$  CPU initializes port and control registers to their default states. To form the internal reset line, the output of the trigger is synchronized with the internal clock. The clock must therefore be running for  $\overline{RESET}$  to function. It requires 4 internal system clocks after reset is detected for the Z8 CPU to reset the internal circuitry. An internal pull-up, combined with an external capacitor of 1  $\mu$ F, provides enough time to properly reset the Z8 CPU (see Figure 23 on page 36). In some cases, the Z8 CPU has an internal POR timer circuit that holds the Z8 CPU in reset mode for a duration ( $T_{POR}$ ) before releasing the device out of reset. On these Z8 devices, the internally generated reset drives the reset pin low for the POR time. Any devices driving the reset line must be open-drained in order to avoid damage from possible conflict during reset conditions. This reset time allows the on-board clock oscillator to stabilize.

To avoid asynchronous and noisy reset problems, the Z8 CPU is equipped with a reset filter of four external clocks (4TpC). If the external reset signal is less than 4TpC in duration, no reset occurs. On the fifth clock after the reset is detected, an internal RST signal is latched and held for an internal register count of 18 external clocks, or for the duration of the external reset, whichever is longer. During the reset cycle,  $\overline{\rm DS}$  is held active low while  $\overline{\rm AS}$  cycles at a rate of the internal system clock. Program execution begins at location 000Ch, 5-10 TpC cycles after  $\overline{\rm RESET}$  is released. For the internal Power-On Reset, the reset output time is specified as  $T_{\rm POR}$ . Refer to specific product specifications for actual values.

Figure 23. Example of External Power-On Reset Circuit

Table 13. ERF Bank 0 Reset Values at RESET

| Register |                                      |   |   |   | В | its |   |   |   |                                                                                                                 |

|----------|--------------------------------------|---|---|---|---|-----|---|---|---|-----------------------------------------------------------------------------------------------------------------|

| (Hex)    | Register Name                        | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 | Comments                                                                                                        |

| 00       | Port 0                               | U | U | U | U | U   | U | U | U | Input mode, output set to push-pull.                                                                            |

| 01       | Port 1                               | U | U | U | U | U   | U | U | U | Input mode, output set to push-pull.                                                                            |

| 02       | Port 2                               | U | U | U | U | U   | U | U | U | Input mode, output set to open drain.                                                                           |

| 03       | Port 3                               | 1 | 1 | 1 | 1 | U   | U | U | U | Standard digital input and output Z86L7X Family Device Port P34-P37 = 0 (Except Z86L70/71/75) All other Z8 = 1. |

| 04-EF    | General-Purpose<br>Registers 04h–EFh | U | U | U | U | U   | U | U | U | Undefined.                                                                                                      |

Table 14. Sample Expanded Register File Bank C Reset Values

| Register |                        |   |   |   |   |   |   |   |   |          |

|----------|------------------------|---|---|---|---|---|---|---|---|----------|

| (Hex)    | Register Name          | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Comments |

| 00       | SPI Compare (SCOMP)    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |          |

| 01       | Receive Buffer (RxBUF) | U | U | U | U | U | U | U | U |          |

| 02       | SPI Control (SCON)     | U | U | U | U | 0 | 0 | 0 | 0 |          |

Table 15. Sample Expanded Register File Bank F Reset Values

| Register |                                |     |   |   | В | its |   |   |   |                                                             |

|----------|--------------------------------|-----|---|---|---|-----|---|---|---|-------------------------------------------------------------|

| (Hex)    | Register Name                  | 7   | 6 | 5 | 4 | 3   | 2 | 1 | 0 | Comments                                                    |

| 00       | Port Configuration             | 1 1 |   | 1 | 1 | 1   | 1 | 1 | 0 | Comparator outputs disabled on Port 3.                      |

|          | (PCON)                         |     |   |   |   |     |   |   |   | Port 0 and 1 output is push–pull.                           |

|          |                                |     |   |   |   |     |   |   |   | Port 0, 1, 2, 3, and oscillator with standard output drive. |

| 0B       | Stop Mode                      | 0   | 0 | 1 | 0 | 0   | 0 | 0 | 0 | Clock divide by 16 off.                                     |

|          | Recovery (SMR)                 |     |   |   |   |     |   |   |   | XTAL divide by 2.                                           |

|          |                                |     |   |   |   |     |   |   |   | POR and/OR External Reset.                                  |

|          |                                |     |   |   |   |     |   |   |   | Stop delay on.                                              |

|          |                                |     |   |   |   |     |   |   |   | Stop recovery level is low, STOP Flag is POR.               |

| 0F       | Watchdog Timer<br>Mode (WDTMR) | U   | U | U | 0 | 1   | 1 | 0 | 1 | 512 TPC for WDT time out, WDT runs during STOP.             |

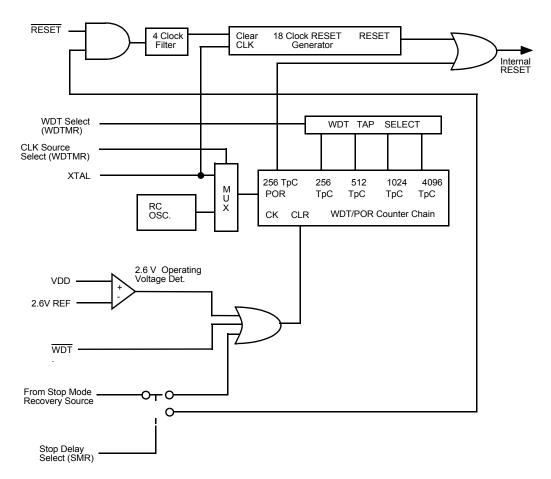

Figure 24. Example of Z8 Reset with RESET Pin, WDT, SMR, and POR

Figure 25. Example of Z8 Reset with WDT, SMR, and POR

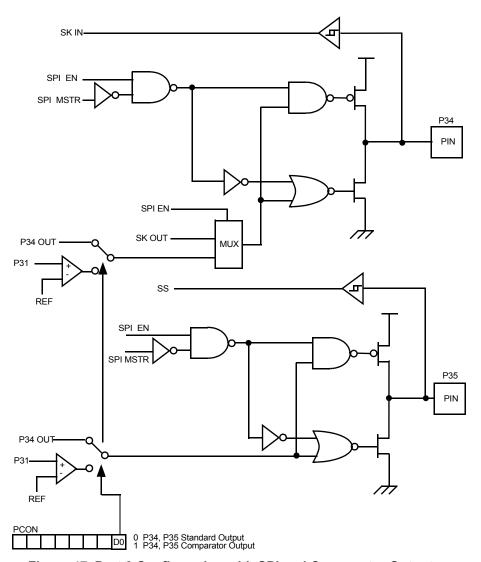

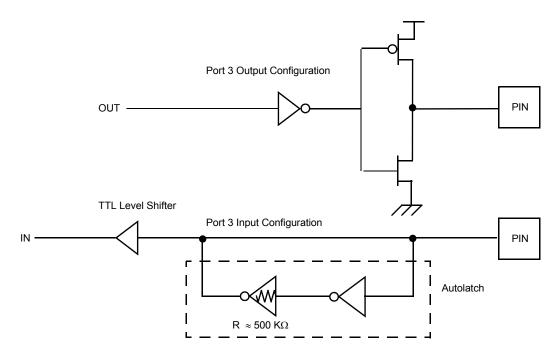

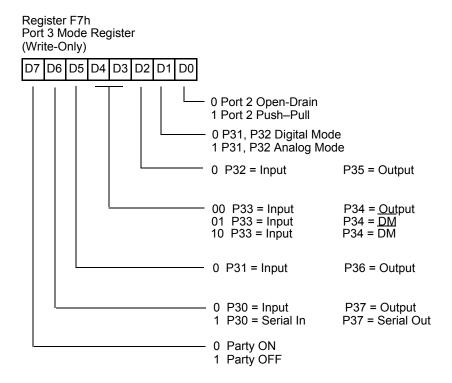

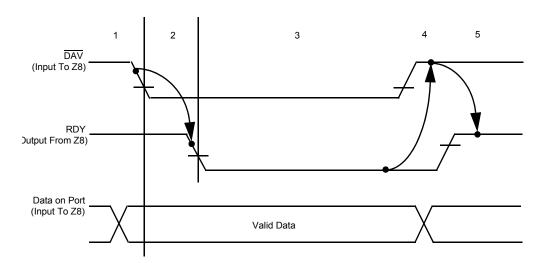

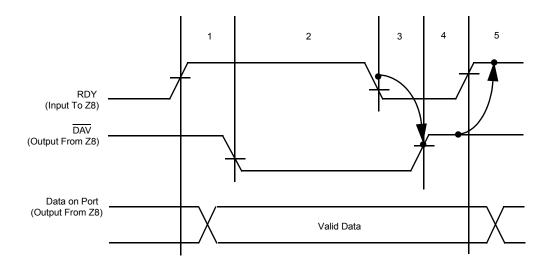

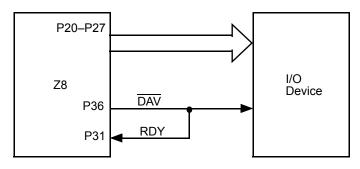

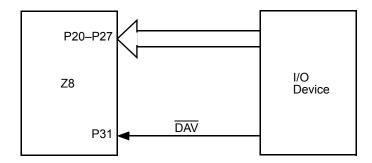

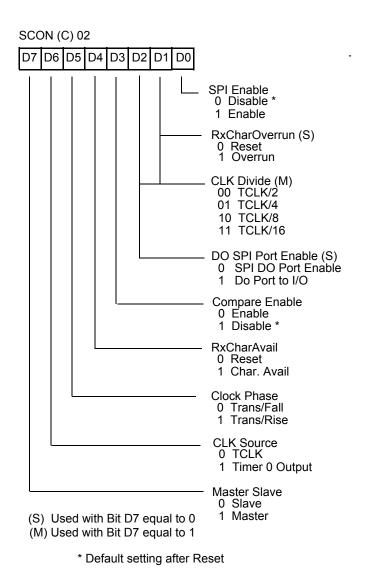

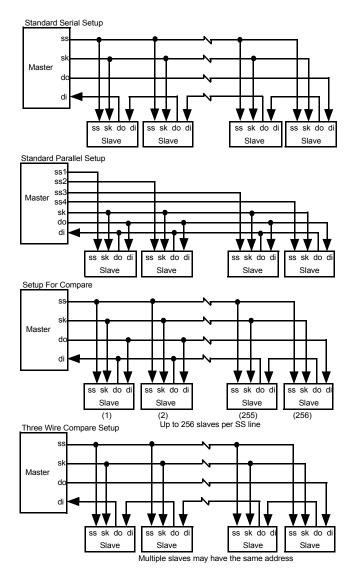

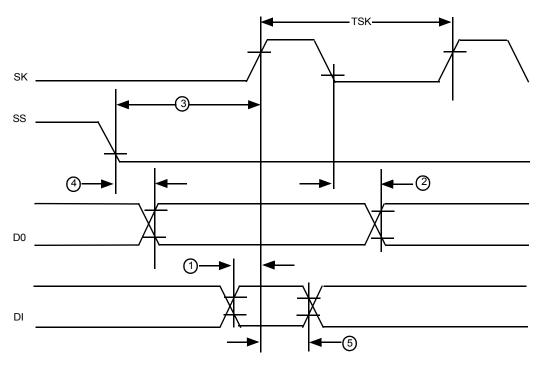

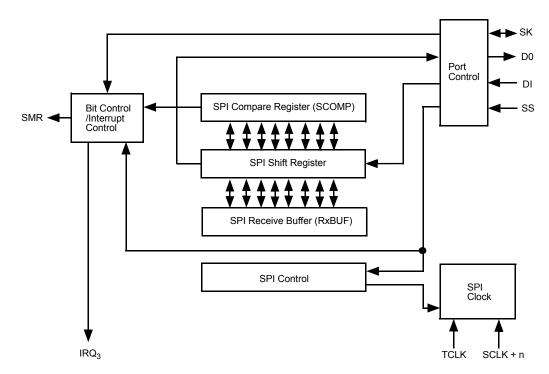

# **Watchdog Timer**