# RM 65 FRMILY

$\bigcirc$

$\bigcirc$

# Single Board Computer (SBC) Module USER'S

MANUAL

Document No. 29801 N09 Order No. 809 Rev. 1 October 1982

# RM 65 FRMILY

# Single Board Computer (SBC) Module USER'S MANUAL

Rockwell International Corporation, 1981 All Rights Reserved Printed in U.S.A. \$2.00 Document No. 29801 N09 Order No. 809 Rev. 1 October 1982

1V

ZZ

# TABLE OF CONTENTS

# Section 1

INTRODUCTION

Page

|             | 1.1   | Purpose/Function                      | 1 - 1 |

|-------------|-------|---------------------------------------|-------|

|             | 1.2   | Features                              | 1-1   |

|             | 1.3   | Characteristics                       | 1-3   |

| No.         | 1.4   | Reference Documents                   | 1-3   |

| 198         | 19.25 |                                       |       |

| 2           | INST  | ALLATION AND OPERATION                |       |

| Service and | 2.1   | Unpacking                             | 2-1   |

|             | 2.2   | Operating Options                     | 2-1   |

|             | and a | 2.2.1 Base Address Selection          | 2-1   |

|             |       | 2.2.2 Bank Selection                  | 2-4   |

|             |       | 2.2.3 PROM/ROM Size Selection         | 2-7   |

|             |       | 2.2.4 Remote RESET Option             | 2-8   |

|             |       | 2.2.5 Clock Source Selection          | 2-8   |

|             |       | 2.2.6 Bank Address Source and Control | 2-9   |

|             |       | 2.2.7 DMA Terminate Control           | 2-9   |

|             | 2.3   | Installing the Module                 | 2-10  |

|             | 2.4   | Removing the Module                   | 2-11  |

| 3           | FUNC  | TIONAL AND INTERFACE DESCRIPTION      |       |

| EAST TAS    |       |                                       |       |

|             | 3.1   | Functional Description                | 3-1   |

|             | 3.2   | Interface Description                 | 3-3   |

|             |       |                                       |       |

| 4           | PROG  | RAMMING CONSIDERATIONS                |       |

|             | 4.1   | General Considerations                | 4-1   |

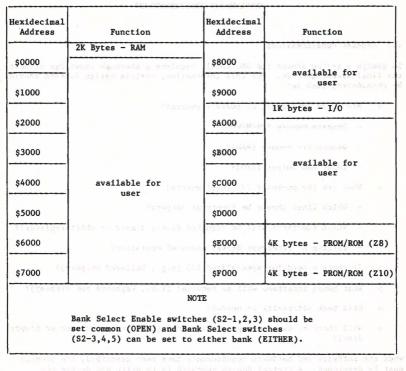

|             | 4.2   | SBC Memory Map                        | 4-1   |

| 1           | 4.3   | Initialization Software               | 4-2   |

|             | 4.4   | DMA Considerations                    | 4-7   |

|             |       |                                       |       |

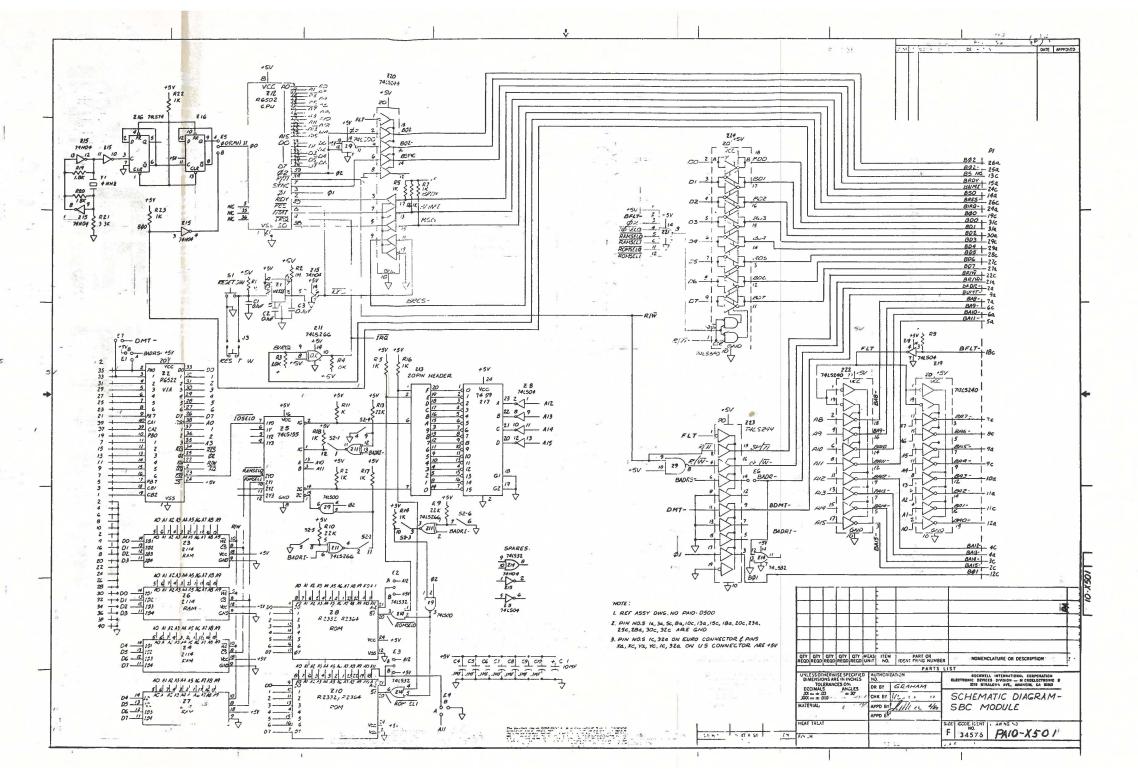

ENCLOSURE A SBC MODULE SCHEMATIC

ii

#### LIST OF FIGURES

| Figure | Title                                           | Page |

|--------|-------------------------------------------------|------|

| 1-1    | SBC Module                                      | 1-2  |

| 1-2    | SBC Module Outline                              | 1-5  |

| 2-1    | SBC Module Detail                               | 2-2  |

| 2-2    | Base Address Selection Header                   | 2-5  |

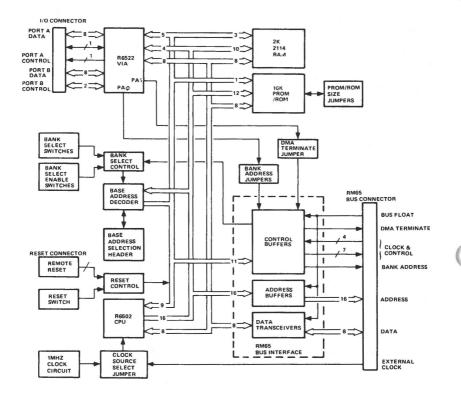

| 3-1    | SBC Module Block Diagram                        | 3-2  |

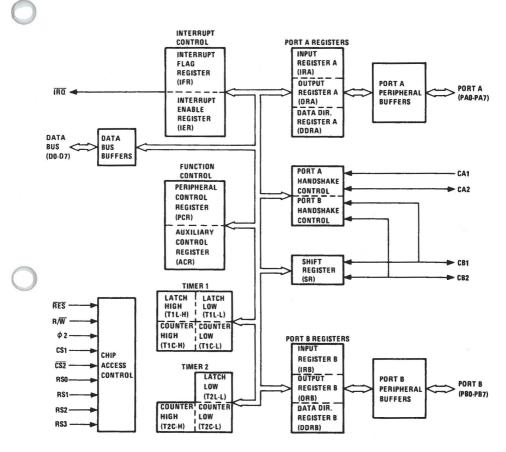

| 4-1    | Versatile Interface Adapter (VIA) Block Diagram | 4-4  |

#### LIST OF TABLES

#### Table Title Page 1-1 SBC Module Physical and Electrical Characteristics ..... 1-4 SBC Module Switches, Header, Jumpers and Connectors ..... 2-1 2 - 32-2 Base Address Selection Header ..... 2-6 2-3 Bank Selection Switch Positions ..... 2-7 2 - 4PROM/ROM Size Selection Jumper Positions ..... 2-8 2-5 2-8 Clock Source Selection Jumper Positions ..... 2-6 Bank Address Source and Control Jumper Positions ..... 2-9 DMA Terminate Control Jumper Positions ..... 2-7 2 - 10Connector Pl (RM 65 Bus) Pin Assignments ..... 3-1 3-4 3-2 Connector J2 (Parallel I/O) Pin Assigments ..... 3-6 1 3-3 Connector J3 (Remote RESET) Pin Assignments ..... 3-7 3-4 Connector P1 (RM 65 Bus) Signal Descriptions ..... 3-8 Connector J2 (Parallel I/O) Signal Descriptions ..... 3-5 1 3-13 4-1 Standard SBC Module Memory Map ..... 4-2 4-2 Memory Map for SBC 1/0 ..... 4-6

Revised 10/82

#### SECTION 1

INTRODUCTION

#### 1.1 PURPOSE/FUNCTION

The RM 65 Single Board Computer module (SBC) is designed for user flexibility. There are provisions for all the necessary elements of single board operation - program memory, read/write memory, input, and output. Additionally there is expansion capability for multi-module applications - flexible memory mapping, bank addressing, and DMA compatability. Being similar both in hardware and software to the AIM 65, the SBC is well supported for system design and development using the AIM 65.

The SBC module allows users to design their products into compact, modular stacks. The SBC module plugs into a single slot in an RM 65 card cage/motherboard and controls other memory and I/O modules. The heart of the SBC module is an R6502 CPU, which is capable of addressing 65K bytes of memory. In addition, the SBC module contains bank address logic which allows addressing of one or two 65K byte memory banks. Sockets on the module accept up to 16K bytes of PROM/ROM. 2K bytes of static RAM are also provided. An R6522 Versatile Interface Adapter (VIA) provides two 8-bit parallel I/O data lines, two 2 bit control lines, two counter-timers and an 8-bit shift register. A base address selection header assigns memory sections to 4K byte blocks. All address, data and control lines are buffered.

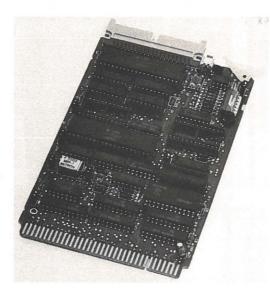

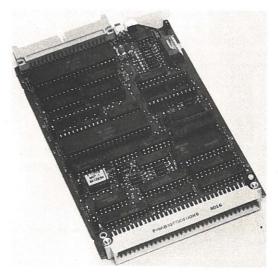

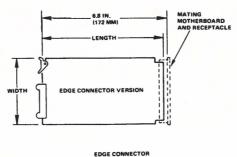

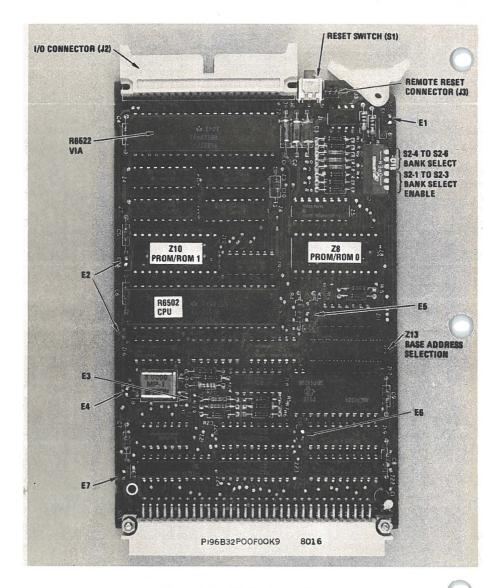

The SBC module is available in a 72-pin Edge Connector version (RM65-1000) and in a 64-pin Eurocard version (RM65-1000E). Both versions are shown in Figure 1-1. The pin assignments for the two versions are identical except the edge connector has four additional pins connected to +5 Vdc and four unused pins (see Table 3-1 for the pin assignments).

#### 1.2 FEATURES

- o Rockwell RM 65 Bus compatible

- o Compact size about 4" x 6-1/2" (100 mm x 160 mm)

- o Fully buffered address, data, and control lines for RM 65 Bus

- o R6502 CPU

- o 2K bytes of R2114 static RAM

- Two sockets for up to 16K bytes of the following PROM/ROM or equivalents

- TI TMS 2516, TMS 2532, and Motorola MCM 68764 PROMs

- Rockwell R2316, R2332, or R2364 ROMs

a. Edge Connector Version

b. Eurocard VersionFigure 1-1. SBC Module

- Two 8-bit parallel bidirectional data ports

- Four control lines

- Two programmable 16-bit counter/timers

- Shift register for serial communications

- Separate switches allow RAM, PROM/ROM, and VIA to be individually dedicated to one or both 65K memory banks

- o Flexible selection of the following

- 2K, 4K or 8K PROM/ROMs

- RAM, PROM/ROM and I/O base address to any 4K byte boundary

- On-board or external bank addressing source

- Programmable DMA Terminate

- On-board or external clock source

- o +5V operation

- o Fully assembled, tested and warranted

#### 1.3 CHARACTERISTICS

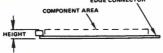

The SBC module physical and electrical characteristics are defined in Table 1-1.

#### **1.4 REFERENCE DOCUMENTS**

Rockwell

Document No.

| 29650N30 | R6500 Programming Manual                |

|----------|-----------------------------------------|

| 29650N31 | R6500 Hardware Manual                   |

| 29650N36 | AIM 65 Microcomputer User's Guide       |

| 29000D47 | R6522 Versatile Interface Adapter (VIA) |

Revised 10/82

### Table 1-1. SBC Module Physical and Electrical Characteristics

| Characteristics                                                   | Value                                                                                               |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Physical Characteristics<br>(See Figure 1-2)                      |                                                                                                     |

| Edge Connector Version                                            |                                                                                                     |

| Width<br>Length<br>Height                                         | 3.9 in. (100 mm)<br>6.5 in. (164 mm)<br>0.56 in. (14 mm)                                            |

| Weight                                                            | 5.3 oz. (150 g)                                                                                     |

| Eurocard Version                                                  |                                                                                                     |

| Width<br>Length<br>Height                                         | 3.9 in. (100 mm)<br>6.3 in. (160 mm)<br>0.56 in. (14 mm)                                            |

| Weight                                                            | 5.6 oz. (160 g)                                                                                     |

| Environment                                                       |                                                                                                     |

| Operating Temperature<br>Storage Temperature<br>Relative Humidity | 0° to 70°C<br>-40°C to 85°C<br>0% to 85% (without condensation)                                     |

| Power Requirements                                                | +5 Vdc <u>+</u> 5% 0.75A (3.5W) - Typical                                                           |

|                                                                   | +5 Vdc <u>+</u> 5% 1.2A (6.0W) - Maximum                                                            |

| Interface Connectors                                              |                                                                                                     |

| RM 65 Bus Connection                                              |                                                                                                     |

| Edge Connector Version<br>Eurocard Version                        | 72-pin edge connector (0.100 in. centers)<br>64-pin plug (0.10 in. centers) per DIN                 |

| Eurocard version                                                  | 41612 (Row b not installed)                                                                         |

| I/O Connector                                                     | 40-pin mass termination connector<br>(0.100 in. centers)<br>Mates to T&B/Ansley 609-4000M or equiv. |

| Remote RESET Connector                                            | 2 vertical pins (0.3 in. high) on 0.200 in. centers                                                 |

|                                                                   |                                                                                                     |

|                                                                   |                                                                                                     |

**Module Dimensions**

Figure 1-2. SBC Module Outline

#### SECTION 2

#### INSTALLATION AND OPERATION

#### 2.1 UNPACKING

Unpack the SBC module from its shipping carton and, referring to the packing list, verify that all of the parts are included. Save the packing material for storing the module.

#### CAUTION

This module contains voltage sensitive items. The module should be stored in an anti-static container when not in use and anyone handling unit should observe antistatic precautions. Damage to the unit may result if anti-static protection is not maintained.

2.2 OPERATING OPTIONS

The switch, header or jumper selectable operating options are:

- o Base Address selection

- o Bank Address selection

- o PROM/ROM Size selection

- o Remote Reset

- o Clock Source selection

- o Bank Address Source

- o DMA Terminate Source

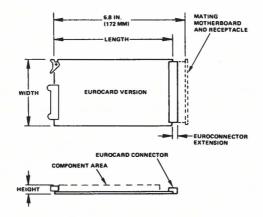

Figure 2-1 identifies the detail on the SBC module. The function of each switch, jumper and connector is identified in Table 2-1 along with reference to the section and/or table that describes its use.

Figure 2-1. SBC Module Detail

## Table 2-1. SBC Module Switches, Header, Jumpers and Connectors

| Category      | Item                 | Description                                                                      | Reference                                |

|---------------|----------------------|----------------------------------------------------------------------------------|------------------------------------------|

| Switches      | S1                   | RESET switch                                                                     | Section 2.2.4                            |

|               | S2<br>-1<br>-2<br>-3 | Bank Select Enable switch for:<br>I/O section<br>RAM section<br>PROM/ROM section | Section 2.2.2<br>Table 2-3               |

|               | S2<br>-4<br>-5<br>-6 | Bank Select switch for:<br>I/O section<br>RAM section<br>PROM/ROM sections       | Section 2.2.2<br>Table 2-3               |

| Header        | Z13                  | Base Address Selection header                                                    | Section 2.2.1<br>Table 2-2<br>Figure 2-2 |

| Jumpers       | E1                   | Bank Address Control jumper                                                      | Section 2.2.6<br>Table 2-6               |

|               | E2                   | Size Selection (4K/8K) for<br>PROM/ROM section 0 (28)                            | Section 2.2.3<br>Table 2-4               |

|               | E3                   | Size Selection (4K/8K) for<br>PROM/ROM Section 1 (Z10)                           |                                          |

|               | E4                   | Size Selection (2K/4K) for<br>PROM/ROM section 1 (Z10)                           |                                          |

|               | E5                   | External Clock Source selection                                                  | Section 2.2.5<br>Table 2-5               |

|               | E6                   | Bank Address Source jumper                                                       | Section 2.2.6<br>Table 2-6               |

| 1999 - 1<br>1 | E7                   | DMA Terminate jumper                                                             | Section 2.2.7<br>Table 2-7               |

| Connectors    | P1                   | RM 65 bus connector                                                              | Tables 3-1 an<br>3-4                     |

|               | J2                   | Parallel I/O connector                                                           | Tables 3-2 and<br>3-5                    |

|               | J3                   | Remote RESET connector                                                           | Section 2.2.4<br>Table 3-3               |

#### 2.2.1 Base Address Selection

The SBC module is segmented into four independent sections:

2K byte RAM section

1K byte I/O section

Two 2K, 4K or 8K byte PROM/ROM sections

A base address that uniquely defines a 4K or 8K byte block must be assigned to each section (or any section may be disabled if not required). No two sections may be assigned a common base address (unless each are dedicated to a different memory bank - see Section 2.2.2). A section is assigned to a base address by installing a jumper between its Section pin and the desired Base Address pin of the Base Address header (Z13 - see Figure 2-1 and Table 2-2). A section is disabled by leaving the Section pin dissconnected.

The RAM section will always be assigned to the lower 2K bytes of the selected 4K block.

The I/O will always be assigned to the lower 1K bytes of the selected 4K block (the first 16 bytes are unique VIA registers, while the remaining locations are redundant).

PROM/ROM Section 1 can be assigned to a 4K or 8K byte block; A 2K PROM/ROM will reside in either the lower 2K bytes of the selected 4K block or in the entire 4K block with 2K images in both the upper and lower half, depending on the position of the 2K/4K Size Selection jumper. PROM/ROM Section 0 can be assigned to a 4K, or an 8K byte block; a 2K PROM/ROM will always reside in the lower 2K bytes of the selected 4K block. An 8k device in either section requires two Base Address jumpers, with one for each 4K segment.

#### 2.2.2 Bank Selection

The SBC module supports RM 65 bank addressing for all on-board memory and I/O. The bank Select Enable switches (S2-1 to S2-3), in conjunction with the Bank Select switches (S2-4 to S2-6), allow the RAM, PROM/ROM, and I/O to be independently assigned common to both 65K memory banks (Bank 0 and Bank 1) or dedicated to a selected memory bank (Bank 0 or Bank 1). The RAM, I/O, and PROM/ROM (both sections together) are each provided with Bank Selection capability.

When OPEN, the Bank Select Enable switch assigns its section (I/O, RAM or PROM/ROM) common to both banks, regardless of the section's Bank Select switch. When the Bank Select Enable switch is CLOSED, the assigned bank is determined by the Bank Select switch. See Table 2-3 for switch assignments and positions.

The two bank structure of the SBC allows two sections to be assigned the same base address, with each in a different dedicated bank.

Revised 10/82

女性别的人情,你说是这些法文的意,这些处理新闻的,如果儿子。"李介蒙,如果接近算

. .

| 2<br>8<br>112 X8<br>9 1 X4<br>9 1 X4     | 19<br>18<br>18                                                  | E000<br>D000                                                                                                   |                                                                                                                                                                                                                                         |

|------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 112 NA<br>1971 NA                        | т.<br>Таби                                                      | D000                                                                                                           |                                                                                                                                                                                                                                         |

|                                          |                                                                 |                                                                                                                |                                                                                                                                                                                                                                         |

| a na carice an constraint of             |                                                                 |                                                                                                                |                                                                                                                                                                                                                                         |

|                                          | 17                                                              | C000                                                                                                           |                                                                                                                                                                                                                                         |

| 60.08                                    |                                                                 |                                                                                                                |                                                                                                                                                                                                                                         |

| BASE                                     | 16                                                              | B000                                                                                                           |                                                                                                                                                                                                                                         |

| ADDRESS                                  |                                                                 |                                                                                                                |                                                                                                                                                                                                                                         |

| SELECTION                                | 15                                                              | A000                                                                                                           |                                                                                                                                                                                                                                         |

| 7.62 .73                                 |                                                                 |                                                                                                                |                                                                                                                                                                                                                                         |

|                                          | 14                                                              | 0000                                                                                                           |                                                                                                                                                                                                                                         |

| 112 14                                   |                                                                 |                                                                                                                |                                                                                                                                                                                                                                         |

| an a | 13                                                              | 8000                                                                                                           |                                                                                                                                                                                                                                         |

| 2                                        | 90.02                                                           |                                                                                                                |                                                                                                                                                                                                                                         |

| ter year many red                        | 12                                                              | 7000                                                                                                           |                                                                                                                                                                                                                                         |

| in epithts mend                          | Sec. 1                                                          |                                                                                                                |                                                                                                                                                                                                                                         |

| 0                                        | 11                                                              | 6000                                                                                                           |                                                                                                                                                                                                                                         |

|                                          | Z13<br>BASE<br>ADDRESS<br>SELECTION<br>HEADER<br>PIN<br>NUMBERS | Z13     16       BASE     ADDRESS       SELECTION     15       HEADER     PIN       PIN     14       13     12 | Z13         16         B000           BASE         ADDRESS         5           SELECTION         15         A000           HEADER         PIN         14         0000           NUMBERS         13         8000         12         7000 |

Figure 2-2. Base Address Selection Header

2-5

Revised 10/82

#### Table 2-2. Base Address Selection Header

| Section                  | Z13 Pin Number |

|--------------------------|----------------|

| RAM                      | 7              |

| PROM/ROM Section 0(28)   | 2              |

| PROM/ROM Section 1 (Z10) | 1              |

| 1/0                      | 6              |

#### a. Section pins

| 4K Base<br>Address | Z13<br>Pin Number | 4K Base<br>Address | Z13<br>Pin Number |

|--------------------|-------------------|--------------------|-------------------|

| 0000               | 14                | 8000               | 13                |

| 1000               | 8                 | 9000               | 3                 |

| 2000               | 5                 | A000               | 15                |

| 3000               | 4                 | B000               | 16                |

| 4000               | 10                | C000               | 17                |

| 5000               | 9                 | D000               | 18                |

| 6000               | 11                | E000               | 19                |

| 7000               | 12                | F000               | 20                |

#### NOTES:

Any section may be disabled by leaving the section pin disconnected.

Two sections may have the same base address only if they are each dedicated to different banks.

#### b. Base Address pins

|                            | Switch Position              |                       |  |  |

|----------------------------|------------------------------|-----------------------|--|--|

| Memory Bank Selected:      | Bank Select<br>Enable Switch | Bank Select<br>Switch |  |  |

| For RAM section            | s2-2                         | s2-5                  |  |  |

| Bank 0 and 1 (common)      | OPEN                         | EITHER                |  |  |

| Bank 0 (lower 65K)         | CLOSED                       | OPEN                  |  |  |

| Bank 1 (upper 65K)         | CLOSED                       | CLOSED                |  |  |

| For I/O section            | S2-1                         | s2-4                  |  |  |

| Bank 0 and 1               | OPEN                         | EITHER                |  |  |

| Bank 0                     | CLOSED                       | OPEN                  |  |  |

| Bank 1                     | CLOSED                       | CLOSED                |  |  |

| For both PROM/ROM sections | S2-3                         | S2-6                  |  |  |

| Bank 0 and 1               | OPEN                         | EITHER                |  |  |

| Bank O                     | CLOSED                       | OPEN                  |  |  |

| Bank 1                     | CLOSED                       | CLOSED                |  |  |

#### Table 2-3. Bank Selection Switch Positions

#### 2.2.3 PROM/ROM Size Selection

The following 2K, 4K, and 8K PROM/ROM devices (or equivalent) can be installed in PROM/ROM section 0 or section 1 (28, 210):

Rockwell R2316 (2K x 8 ROM) Intel 2716 (2K x 8 EPROM)

Rockwell R2332 (4K x 8 ROM) Texas Instruments 2532 (4K x 8 EPROM)

Rockwell R2364A (8K X 8 ROM) Motorola MCM68764 (8K x 8 EPROM)

The 4K/8K size selection for PROM/ROM section 0 (Z8) uses jumper E2. The 4K/8K size selection for PROM/ROM section 1 (Z10) uses jumper E3, while the | 2K/4K selection uses jumper E4. The jumper positions are shown in Table 2-4.

Revised 10/82

|                        | Vei                                                              | onnector<br>rsion                                                                                                                                                                                                                       | Euroconnector<br>Version                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROM/ROM               | Jumper                                                           | Position                                                                                                                                                                                                                                | Jumper                                                                                                                                                                                                                                                                                                                                         | Position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2K                     | E2A                                                              | Off                                                                                                                                                                                                                                     | E2A                                                                                                                                                                                                                                                                                                                                            | On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (see note 1)           | E2B                                                              | On                                                                                                                                                                                                                                      | E2B                                                                                                                                                                                                                                                                                                                                            | Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4K                     | E2A                                                              | Off                                                                                                                                                                                                                                     | E2A                                                                                                                                                                                                                                                                                                                                            | On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                        | E2B                                                              | On                                                                                                                                                                                                                                      | E2B                                                                                                                                                                                                                                                                                                                                            | Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8K                     | E2A                                                              | On                                                                                                                                                                                                                                      | E2A                                                                                                                                                                                                                                                                                                                                            | Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| oga i narra keogramina | E2B                                                              | Off                                                                                                                                                                                                                                     | E2B                                                                                                                                                                                                                                                                                                                                            | On                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2K                     | E3                                                               | В                                                                                                                                                                                                                                       | E3                                                                                                                                                                                                                                                                                                                                             | B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| (see Note 2)           | E4                                                               | A or B                                                                                                                                                                                                                                  | E4                                                                                                                                                                                                                                                                                                                                             | A or B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4K                     | E3                                                               | В                                                                                                                                                                                                                                       | E3                                                                                                                                                                                                                                                                                                                                             | B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | E4                                                               | A                                                                                                                                                                                                                                       | E4                                                                                                                                                                                                                                                                                                                                             | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8K                     | E3                                                               | A                                                                                                                                                                                                                                       | E3                                                                                                                                                                                                                                                                                                                                             | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | E4                                                               | A                                                                                                                                                                                                                                       | E4                                                                                                                                                                                                                                                                                                                                             | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                        | 2K<br>(see note 1)<br>4K<br>8K<br>2K<br>(see Note 2)<br>4K<br>8K | 2K         E2A           (see note 1)         E2B           4K         E2A           E2B         E2A           8K         E2A           2K         E3           (see Note 2)         E4           4K         E3           E4         E4 | 2K         E2A         Off           (see note 1)         E2B         On           4K         E2A         Off           E2B         On         E2B           8K         E2A         Off           2K         E3         B           (see Note 2)         E4         A or B           4K         E3         B           4K         E3         A | 2K         E2A         Off         E2A           (see note 1)         E2B         On         E2B           4K         E2A         Off         E2B           4K         E2A         Off         E2B           8K         E2A         On         E2B           8K         E2A         On         E2B           2K         E2B         On         E2B           3K         E2A         On         E2B           2K         E3         B         E3           (see Note 2)         E4         A or B         E4           4K         E3         B         E3           E4         A         E4         A           8K         E3         A         E3           E4         A         E4         A           E4         A         E4         A |

#### Table 2-4. PROM/ROM Size Selection Jumper Positions

E4 = A: Enabled in lower half of the 4K-byte address space (\$X000-\$X7FF) only (pin 18 = All = 0).

E4 = B: Enabled in upper half of the 4K-byte address space

(\$X800-\$XFFF) only (pin 18 = +5V = 1).

#### 2.2.4 Remote RESET Option

The SBC module provides an on-board RESET switch. When depressed, a hardware reset is generated for the R6502 (CPU), R6522 (VIA), and driven onto the RM 65 bus. A remote reset connector (J3) is provided to allow an additional switch to be mounted separate from the module. This connector parallels the on-board RESET switch, so activating either, or both, will generate a RESET.

#### 2.2.5 Clock Source Selection

The SBC module uses an on-board crystal controlled oscillator which provides a l MHz clock reference for the module and the RM 65 bus system clocks (BØ1, BØ2, BØ2/). An external clock from the RM 65 Bus (BØ0) can be selected as the clock reference by the Clock Source Selection jumper (E5). The positions for the Clock Source Selection jumper are shown in Table 2-5.

| Clock Source                                    | Jumper Position |

|-------------------------------------------------|-----------------|

| Internal Clock Reference<br>BØl = 1 MHz         | E5 = A          |

| External Clock Source (BØO)<br>BØ1 $\leq$ 1 MHz | E5 = B          |

Table 2-5. Clock Source Selection Jumper Positions

Revised 10/82

#### 2.2.6 Bank Address Source and Control

The SBC module provides control of the source of the Bank Address signal (BADR/) on the RM 65 bus. The Bank Address Source jumper (E6) allows the bank address signal source to be changed, either generated by the SBC module to drive the RM 65 bus, or received from the bus. When the SBC module is the source of the bank address signal, the Bank Address Control jumper (E1) selects between always Bank 0, or bank switching using the VIA device (peripheral port A, bit 0). Table 2-6 summarizes the jumper positions.

#### NOTE

If the VIA device is chosen to control the bank address line, the I/O must be bank selected common to both banks.

Table 2-6. Bank Address Source and Control Jumper Positions

| Bank Address BADR/<br>Source Direction Jumper Position |        |                        |

|--------------------------------------------------------|--------|------------------------|

| Fixed to Bank 0<br>(from SBC module)                   | Output | E1 = B E6 INSTALLED    |

| Controlled by VIA<br>(from SBC module)                 | Output | E1 = /. E6 INSTALLED   |

| External Control<br>(from RM 65 Bus)                   | Input  | E1 = EITHER E6 REMOVED |

#### 2.2.7 DMA Terminate Control

The SBC module will always source the DMA Terminate (BDMT/) signal onto the RM 65 bus. The DMA Terminate Control Jumper (E7) allows this signal to be always inactive (forced to a logic 1) or to be controlled by the VIA device (peripheral port A, bit 1). Table 2-7 shows the possible jumper positions.

Table 2-7. DMA Terminate Control Jumper Positions

| DMA Terminate<br>Control (BDMT/)     | Jumper Position |

|--------------------------------------|-----------------|

| Fixed to inactive level<br>(logic l) | E7 REMOVED      |

| Controlled by VIA                    | E7 INSTALLED    |

#### 2.3 INSTALLING THE MODULE

Before installing the module, ensure that it is not damaged and is free of grease, dirt, or other foreign matter. Installation is accomplished as follows:

#### CAUTION

Prior to module installation, turn off power to the RM 65 Bus and to any interfacing external equipment.

- a. Based on the system memory map and requirements (refer to Section 4), select the proper module operating options by performing the following steps:

- Install the required PROM or ROM devices into sockets Z8 and Z10, and position jumpers E2, E3 and E4 as required (refer to Section 2.2.3, 2.2.4, and Table 2-4, 2-5).

- (2) Select the module base addresses with header Z13 (refer to Section 2.2.1, Table 2-2, and Figure 2-1).

- (3) Select common or dedicated memory bank operation for RAM, PROM/ROM, and I/O sections by positioning switches S2-1 to S2-6 (refer to Section 2.2.2 and Table 2-3).

- (4) Select the system clock source by positioning jumper E5 (refer to Section 2.2.5 and Table 2-6).

- (5) Select the proper bank addressing source by positioning jumpers E1 and E6 (refer to Section 2.2.6 and Table 2-6).

- (6) Select the proper DMA terminate source by positioning jumper E7 (refer to Section 2.2.7 and Table 2-7).

b. Align pin Wa (Edge Connector version) or pin la (Eurocard version) of the module with the corresponding pin on the mating RM 65 bus receptacle.

#### CAUTION

RM 65 connectors are keyed to prevent improper module connection. If the module does not insert into the receptacle with moderate pressure applied, check the orientation and connector alignment of the module. Forcing module improperly into the receptacle will damage the receptacle and/or the module.

- c. Insert the module into the desired card slot and position it above the mating receptacle.

- d. Press in firmly on the end of module until all pins are securely seated.

- e. Connect the required cables to J2 (Parallel I/O) and J3 (Remote RESET) | I/O connectors on the SBC module (see Figure 2-1).

NOTE

Interface cables that connect to the SBC module are supplied by the user.

f. Reapply power to the RM 65 bus.

2.4 REMOVING THE MODULE

- Turn-off power to the RM 65 bus and any interfacing external equipment.

- b. Disconnect the cables from the I/C connectors.

- c. Lift up on the module ejector tab to release the module from the mating receptacle. Pull the module straight back until it is free from the card slot guides.

Revised 10/82

#### SECTION 3

#### FUNCTIONAL AND INTERFACE DESCRIPTION

#### 3.1 FUNCTIONAL DESCRIPTION

The block diagram in Figure 3-1 identifies the SBC module functions and interface signals.

The R6502 Central Processing Unit (CPU) is the heart of the SBC module and any interfacing modules connected to the RM 65 Bus. The R6502 performs all program execution by means of the address, data, control, and timing lines.

The Clock Circuit uses a 4 MHz crystal-controlled oscillator which is divided by four to provide a stable 1 MHz clock reference. The Clock Source Selection jumper chooses between the internal clock reference or an external clock ( $B\emptyset$ 0) as the source for the R6502 and the derived system clocks ( $B\emptyset$ 1, $B\emptyset$ 2, $B\emptyset$ 2/).

The Reset Control circuit conditions the Reset signal for the SBC module and the Bus. A reset can be generated either by the on-board RESET switch (S1) or by a remote RESET switch (connected to J3). This circuitry also generates a reset automatically, upon power-up. The Reset signal (RES) is transferred to the R6502 CPU and R6522 VIA devices, as well as buffered and driven onto the Bus (BRES/).

The Bank Select Control circuit detects when the SBC module's assigned memory bank is addressed, by comparing the Bank Address signal (BADR/) to the Bank Select Enable (S2-1 to S2-3) and Bank Select (S2-4 to S2-6) switches. The Bank Select Enable Switches allow all on-board PROM/ROM, RAM, and VIA to be independently assigned common to both Bank 0 (lower 65K) and Bank 1 (upper 65K), or dedicated to either Bank 0 or Bank 1 as assigned by the Bank Select switches.

The Bank Address jumpers choose the source and control for BADR/. The Bank Address source jumper (E6) determines whether BADR/ is generated by the SBC module (driven onto the Bus) or generated by another module (received from the Bus). When the SBC module is the source, the Bank Address Control jumper (E1) allows BADR/ to be always in Bank 0 (forced to a logic 1) or to be selectable to either bank, under control of the VIA device (peripheral port A, bit 0).

The Base Address Decoder uses the six most significant address bits (BAO/ - BA15/), the bank address signal, and the Base Address Selection header (Z13) to generate chip selects for the on-board PROM/ROM (ROMSELO, ROMSELI), RAM (RAMSELO, RAMSELI), and VIA. The RAM and VIA can be independently mapped into any 4K block of the selected 65K bank. The PROM/ROMs may be mapped into any 4K or 8K block of the selected bank.

The 16K PROM/ROM section has two sockets which can accept 2K, 4K or 8K PROM/ROM devices. The size and type of PROM or ROM is specified by the Base Address Selection header and the PROM/ROM Size jumpers (E2,E3,E4).

Figure 3-1. SBC Module Block Diagram

The 2K RAM section uses four 1K x 4 R2114 RAM devices to provide on-board read/write memory.

The R6522 Versatile Interface Adapter (VIA) provides input-output capability to the SBC Module. The VIA provides two 8-bit I/O ports, each with two control lines. Both ports and the control lines are brought out to a connector for user applications.

The SBC Module can control up to 15 additional support modules by means of the RM 65 Bus. There are three groups of signals on the RM 65 Bus: clock and control, data, and address.

The Data Transceivers invert and transfer eight bits of parallel data (BDO/-BD7/) between the SBC Module and the RM 65 bus. The direction of the transceivers is controlled by the read/write signal from the R6502. The transceivers are disabled (tri-stated) when the on-board PROM/ROM, RAM, or VIA is addressed or when the Bus Float signal (BFLT/) from the RM 65 Bus is active.

The Address Buffers invert and transfer 16 parallel address bits (BAO/-BA15/) from the SBC Module to the RM 65 bus. These buffers are disabled when BFLT/ is active.

The DMA Terminate jumper (E7) allows the DMA Terminate signal (BDMT/) to be always inactive (forced to a logic l) or to be controlled by the VIA device (peripheral port A, bit l).

The Control Buffers buffer all control and clock signals between the SBC Module and the RM 65 bus. The Non-Maskable Interrupt (BRNMI/), Interrupt Request (BIRQ/), Set Overflow (BSO/), External Clock (BØO), Ready (BRDY) and Bus Float (BFLT/) input lines are buffered coming from the RM 65 bus into the SBC Module. The DMA Terminate (BDMT/), Reset (BRES/) and Phase 1 Clock (BØ1) output lines are always driven from the SBC Module onto the RM 65 Bus. The other six output lines for Read/Write (BR/W, BR/W/), Phase 2 Clock (BØ2,BØ2/), Sync (BSYNC), and Bank Address (BADR/) are also buffered, but are disabled when BFLT/ is active.

#### 3.2 INTERFACE DESCRIPTION

Table 3-1 lists pin connections for I/O signals transferred between the SBC module connector Pl and the RM 65 Bus.

Table 3-2 lists pin connections for the VIA device I/O signals transferred on connector J2.

Table 3-3 lists the pin connections for the remote RESET switch on connector J3.

Tables 3-4 and 3-5 describe all I/O signals (Pl and J2) in detail.

Revised 10/82

### Table 3-1. Connector P1 (RM 65 Bus) Pin Assignments

| Pin | Signal<br>Mnemonic | Signal Name              | Pl Input/Output |

|-----|--------------------|--------------------------|-----------------|

| Wa  |                    | Not Connected (See Note) |                 |

| Wc  |                    | Not Connected (See Note) |                 |

| Ха  | +5V                | +5 Vdc (See Note)        |                 |

| Хc  | +5V                | +5 Vdc (See Note)        |                 |

| la  | GND                | Ground                   |                 |

| lc  | +5V                | +5 Vdc                   |                 |

| 2a  | BADR/              | Buffered Bank Address    | 1/0             |

| 2c  | BA15/              | Buffered Address Bit 15  | 0               |

| 3a  | GND                | Ground                   |                 |

| 3c  | BA14/              | Buffered Address Bit 14  | 0               |

| 4a  | BA13/              | Buffered Address Bit 13  | 0               |

| 4c  | BA12/              | Buffered Address Bit 12  | 0               |

| 5a  | BA11/              | Buffered Address Bit 11  | 0               |

| 5c  | GND                | Ground                   |                 |

| 6a  | BA10/              | Buffered Address Bit 10  | 0               |

| 6c  | BA9/               | Buffered Address Bit 9   | 0               |

| 7a  | BA8/               | Buffered Address Bit 8   | 0               |

| 7c  | BA7/               | Buffered Address Bit 7   | 0               |

| 8a  | GND                | Ground                   |                 |

| 8c  | BA6/               | Buffered Address Bit 6   | 0               |

| 9a  | BA5/               | Buffered Address Bit 5   | 0               |

| 9c  | BA4/               | Buffered Address Bit 4   | 0               |

| 10a | BA3/               | Buffered Address Bit 3   | 0               |

| 10c | GND                | Ground                   |                 |

| lla | BA2/               | Buffered Address Bit 2   | 0               |

| llc | BA1/               | Buffered Address Bit 1   | 0               |

| 12a | BAO/               | Buffered Address Bit O   | 0               |

| 12c | BØ1                | Buffered Phase 1 Clock   | 0               |

| 13a | GND                | Ground                   |                 |

| 13c | BSYNC              | Buffered Sync            | 0               |

| 14a | BSO                | Buffered Set Overflow    | I               |

# Table 3-1. Connector Pl (RM 65 Bus) Pin Assignments (Continued)

| 1    | 1                  |                                 | 1               |

|------|--------------------|---------------------------------|-----------------|

| Pin  | Signal<br>Mnemonic | Signal Name                     | Pl Input/Output |

| 14c  | BDRQ1/             | Buffered DMA Request 1          | Not Used        |

| 15a  | BRDY               | Buffered Ready                  | I               |

| 15c  | GND                | Ground                          |                 |

| 16a  |                    | User Spare 1                    | Not Used        |

| 16c  | -12V/-V            | -12 Vdc/-V                      | Not Used        |

| 17a  | +12V/+V            | +12 Vdc/+V                      | Not Used        |

| 17c  |                    | User Spare 2                    | Not Used        |

| 18a  | GND                | Ground                          |                 |

| 18c  | BFLT/              | Buffered Bus Float              | I               |

| 19a  | BDMT/              | Buffered DMA Terminate          | 0               |

| 19c  | BØ0                | Buffered External Phase 0 Clock | I               |

| 20a  |                    | User Spare 3                    | Not Used        |

| 20c  | GND                | Ground                          |                 |

| 21a  | BR/W/              | Buffered Read/Write "Not"       | 0               |

| 21c  |                    | System Spare                    | Not Used        |

| 22a  | BDRQ2/             | Buffered DMA Request 2          | Not Used        |

| 22c  | br/W               | Buffered Read/Write             | 0               |

| 23a  | GND                | Ground                          |                 |

| 23c  | BACT/              | Buffered Bus Active             | Not Used        |

| 24a  | BIRQ/              | Buffered Interrupt Request      | I               |

| 24c  | BNMI/              | Buffered Non-Maskable Interrupt | I               |

| 25a  | BØ2/               | Buffered Phase 2 "Not" Clock    | 0               |

| 25c  | GND                | Ground                          |                 |

| 26a  | BØ2                | Buffered Phase 2 Clock          | 0               |

| 26c  | BRES/              | Buffered Reset                  | 0               |

| 27a  | BD7/               | Buffered Data Bit 7             | 1/0             |

| 27 c | BD6/               | Buffered Data Bit 6             | 1/0             |

| 28a  | GND                | Ground                          |                 |

| 28c  | BD5/               | Buffered Data Bit 5             | 1/0             |

| 29a  | BD4/               | Buffered Data Bit 4             | 1/0             |

| 29c  | BD3/               | Buffered Data Bit 3             | 1/0             |

Table 3-1. Connector P1 (RM 65 Bus) Pin Assignments (Continued)

4

.#

| 30a |      |                          |       |

|-----|------|--------------------------|-------|

|     | BD2/ | Buffered Data Bit 2      | 1/0   |

| 30c | GND  | Ground                   |       |

| 31a | BD1/ | Buffered Data Bit 1      | 1/0   |

| 31c | BDO/ | Buffered Data Bit O      | 1/0   |

| 32a | +5V  | +5 Vdc                   |       |

| 32c | GND  | Ground                   |       |

| Ya  | +5V  | +5 Vdc (See Note)        |       |

| Yc  | +5V  | +5 Vdc (See Note)        |       |

| Za  |      | Not Connected (See Note) |       |

| Zc  |      | Not Connected (See Note) | - 6.6 |

|     |      | NOTE                     |       |

## Table 3-2. Connector J2 (Parallel I/O) Pin Assignments

| Pin | Signal<br>Mnemonic | Signal Name                 | Input/Output |

|-----|--------------------|-----------------------------|--------------|

| 1   | CB2                | Peripheral B, Control No. 2 | 1/0          |

| 3   | CB1                | Peripheral B, Control No. 1 | 1/0          |

| 5   | PB7                | Peripheral B Port, Bit 7    | 1/0          |

| 7   | PB6                | Peripheral B Port, Bit 6    | 1/0          |

| 9   | PB5                | Peripheral B Port, Bit 5    | 1/0          |

| 11  | PB4                | Peripheral B Port, Bit 4    | 1/0          |

| 13  | PB3                | Peripheral B Port, Bit 3    | 1/0          |

| 15  | PB2                | Peripheral B Port, Bit 2    | 1/0          |

| 17  | PB1                | Peripheral B Port, Bit 1    | 1/0          |

|     |                    |                             |              |

Revised 10/82

1

Table 3-2. Connector J2 (Parallel I/O) Pin Assignments (Continued)

-0-

4

| Pin | Signal<br>Mnemonic | Signal Name                                   | Input/Output |

|-----|--------------------|-----------------------------------------------|--------------|

| 19  | PBO                | Peripheral B Port, Bit 0                      | 1/0          |

| 21  | PA7                | Peripheral A Port, Bit 7                      | 1/0          |

| 23  | PA6                | Peripheral A Port, Bit 6                      | 1/0          |

| 25  | PA5                | Peripheral A Port, Bit 5                      | 1/0          |

| 27  | PA4                | Peripheral A Port, Bit 4                      | 1/0          |

| 29  | PA3                | Peripheral A Port, Bit 3                      | 1/0          |

| 31  | PA2                | Peripheral A Port, Bit 2                      | 1/0          |

| 33  | PA1                | Peripheral A Port, Bit 1                      | 1/0          |

| 35  | PAO                | Peripheral A Port, Bit O                      | 1/0          |

| 37  | CA2                | Peripheral A, Control No. 2                   | 1/0          |

| 39  | CA1                | Peripheral A, Control No. 1                   | I            |

|     | All eve            | NOTE<br>en pins 2-40 are connected to Ground. | 1            |

Table 3-3. Connectors J3 (Remote RESET) Pin Assignments

| Pin    | Signal Name                                                                                | Input/Output |

|--------|--------------------------------------------------------------------------------------------|--------------|

| 1<br>2 | RESET<br>Ground                                                                            | I            |

|        | NOTES                                                                                      | -            |

|        | <ol> <li>The Remote RESET switch is in parallel with<br/>on-board reset switch.</li> </ol> | the          |

|        | 2. Pin 1 is the pin closest to the ejector tab.                                            |              |

Revised 10/82

1

Table 3-4. Connector P1 (RM 65 Bus) Signal Description

-

. \*

1

| Mnemonic     | Signal Name and Signal Description                                                                                                                                                                                                                                               | Type of<br>Drive |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|              | NOTE: All signals interfaced to and from the SBC module are driven at TTL voltage levels.                                                                                                                                                                                        |                  |

| +5V          | +5V dc supplied to the SBC module via the RM 65 Bus.                                                                                                                                                                                                                             |                  |

| GND          | Ground                                                                                                                                                                                                                                                                           |                  |

|              | System ground.                                                                                                                                                                                                                                                                   |                  |

| BAO/ - BA15/ | Buffered Address Bits 0-15                                                                                                                                                                                                                                                       |                  |

|              | Sixteen address lines transfer an inverted<br>16-bit parallel address from the Address<br>Buffers in the SBC module onto the                                                                                                                                                     | TS               |

|              | Bus. The Address Buffers are disabled (tri-state) when BFLT/ is active.                                                                                                                                                                                                          |                  |

| BDO/ - BD7/  | Buffered Data Bits 0-7                                                                                                                                                                                                                                                           |                  |

|              | Eight bidirectional inverted data lines 8-bit<br>data bytes between the Data Transceivers in<br>the SBC module and the Bus. The<br>Data Transceivers are disabled (tri-state)<br>when BFLT/ is active.                                                                           | TS               |

| BADR/        | Buffered Bank Address                                                                                                                                                                                                                                                            |                  |

|              | If on-board bank addressing is used, this<br>line transfers the BADR/ signal from the SBC<br>module onto the Bus. The level of<br>BADR/ is either programmed into the VIA device<br>or is fixed to a high level (Bank O). BADR/<br>is disabled (tri-state) when BFLT/ is active. | TS               |

|              | If external bank addressing is used, this line<br>transfers the BADR/ signal from the<br>Bus into the SBC module.                                                                                                                                                                |                  |

|              | A high BADR/ signal addresses the lower 65K<br>(Bank 0) memory bank; a low BADR/ signal<br>addresses the upper 65K (Bank 1) memory bank.                                                                                                                                         |                  |

0

4

٩.

| Mnemonic | Signal Name and Signal Description                                                                                                                                                                                                                                                                                                                    | Type of<br>Drive |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| BØ1      | Buffered Phase 1 Clock<br>The BØ1 signal is the system clock generated<br>by the SBC module for the Bus.                                                                                                                                                                                                                                              | TP               |