# R6500 Microcomputer System APPLICATION NOTE

# Interfacing R6500 Microprocessors To a Floppy Disk Controller

### **PURPOSE**

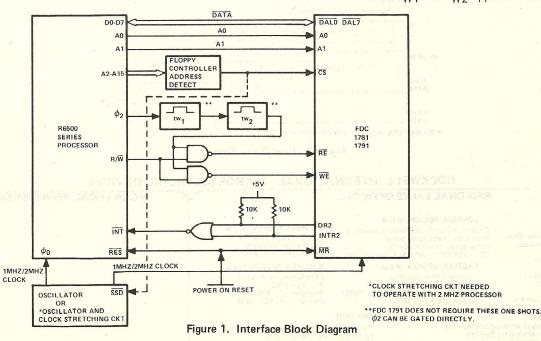

Microprocessors in the R6500 family can operate with a wide variety of special-purpose peripheral controller devices. This Application Note describes the interface between an R6500 microprocessor and either of two Western Digital Floppy Disk Formatter/Controller devices, FDC 1781 and FDC 1791. The interface to the FDC 1781 requires a pair of one-shots, whereas the FDC 1791 can be interfaced directly. In both cases, the processor access time is one cycle.

## DESCRIPTION

The basic interface for both Western Digital devices is shown in Figure 1. Data is passed between the R6500 microprocessor and the floppy disk controller on an 8-bit, bi-directional data bus. Address bus lines A0 and A1 select the FDC registers to be accessed. The remaining Address Bus lines, A2 through A15, can be used to generate a Chip Select signal  $\overline{(CS)}$  when the FDC has been addressed. The  $\emptyset 2$  clock from the processor is used to generate strobes  $\overline{RE}$  and  $\overline{WE}$ , for reading and writing the FDC registers.

### TIMING

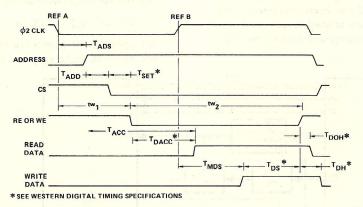

R6500 processors that run on a 1-MHz clock with 50-percent duty cycle will produce  $\emptyset_2$  clock up and down times (PHW $\emptyset_2$ ) of 470 ns minimum. Since the Western Digital FDC 1791 device requires Read and Write pulse widths ( $\overline{\text{RE}}$  and  $\overline{\text{WE}}$ , respectively) of 400 ns, the  $\emptyset_2$  clock is adequate to generate these pulses directly. However, the FDC 1781 requires a minimum pulse width of 500 ns for both  $\overline{\text{RE}}$  and  $\overline{\text{WE}}$ , so some additional strobe-generation circuitry must be included in that interface.

This circuitry is comprised of two one-shots,  $t_{W1}$  and  $t_{W2}$ , in which  $t_{W1}$  determines the start of the pulse and  $t_{W2}$  determines the width of the pulse. The limiting equation for  $t_{W1}$  is:

$T_{ADS} + T_{ADD} + 50 < t_{W1} < 475 \text{ ns}$  (Equation 1) where  $T_{ADS} = Address$  Setup Time from R6500 (225 ns max)

TADD = Address Detect Delay Time

and the limiting equation for tw2 is:

$$500 \text{ ns} < t_{W2} < 1000 \text{ ns} - t_{W1}$$

(Equation 2)

A simple way to guarantee that the timing requirements are met is to make t<sub>W1</sub> and t<sub>W2</sub> approach their respective

lower bounds. The Write cycle timing is satisfied when the Read cycle timing is satisfied, except that the  $t_{\rm W2}$  pulse should be made wide enough to allow the Write data to have adequate setup time. The constraints are reflected in this equation:

(Equation 3)

Time  $t_{W1}$  should be made as narrow as possible, with  $t_{W2}$  widened to satisfy Equations 1 and 2. Figure 2 summarizes the timing relationships.

# INTERFACING 2-MHZ R6500 MICROPROCESSORS

The interface described is based on a 1-MHz R6500 microprocessor. To use a 2-MHz microprocessor (R6500A series), a clock stretching circuit is necessary. This circuit is described in a separate Application Note, "R650X Clock Stretching for Use with Slower Peripherals", Rockwell Document No. R6500N07.

YOUR LOCAL REPRESENTATIVE

#### WESTERN DIGITAL TIMING SPECIFICATIONS

| Characteristic                           | Symbol           | Min          | Max               | Units |

|------------------------------------------|------------------|--------------|-------------------|-------|

| Read Data Access Time, from RE           | TDACC            | e shaennes y | 350               | ns    |

| Read Data Hold Time, from RE             | T <sub>DOH</sub> | 50           |                   | ns    |

| RE Pulse Width For FDC 1781 For FDC 1791 | T <sub>RE</sub>  | 500<br>400   |                   | ns    |

| Write Data Hold Time, from WE            | T <sub>DH</sub>  | 20           | percent of the fi | ns    |

| Data Setup Time to WE                    | T <sub>DS</sub>  | 250          |                   | ns    |

| WE Pulse Width For FDC 1781 For FDC 1791 | TWE              | 350<br>350   | Kot               | ns    |

| Setup Address and CS to WE               | T <sub>SET</sub> | 50           |                   | ns    |

NOTE: For R6500 timing specifications, refer to the R6500 Microprocessors Data Sheet, Rockwell Document No. 29000D39.

Figure 2. Read/Write Timing

#### **ROCKWELL INTERNATIONAL - MICROELECTRONIC DEVICES**

## **REGIONAL SALES OFFICES**

#### CENTRAL REGION, U.S.A.

Contact Robert O. Whitesell & Associates 6691 East Washington Street Indianapolis, Indiana 46219 (317) 359-9283 Attn. Milt Gamble, Mgr.

### EASTERN REGION, U.S.A.\*

Carolier Office Building 850-870 U.S. Route 1 North Brunswick, New Jersey 08902 Phone: (201) 246-3630

# Also Applications Centers EUROPE

Rockwell International Corp. Microelectronic Devices P.O. Box 3669 Anaheim, Ca. 92803 U.S.A.

Phone: (714) 632-0950 TWX: 910-591-1698

HOME OFFICE\*

Rockwell International GmbH Microelectronic Devices Fraunhoferstrasse 11 D-8033 Munchen-Martinsried Germany Phone: (089) 859-9575 Telex: 0521/2650

#### MIDWEST REGION, U.S.A.

1011 E. Touhy Avenue, Suite 245 Des Plaines, IL 60018 Phone: (312) 297-8862

#### WESTERN REGION, U.S.A.

3310 Miraloma Avenue P.O. Box 3669 Anaheim, Ca. 92803 Phone: (714) 632-0950

#### FAR EAST

Rockwell International Overseas Corp. Ichiban-cho Central Building 22-1 Ichiban-cho, Chiyoda-ku Toyko 102, Japan Phone: 265-8808 Telex: J22198

808