#### The IMSAI 8080.

# A commercial yet personally affordable computer.

If you thought you could never afford a computer at home, think again. The IMSAI 8080 is built for rugged industrial performance. Yet its prices are competitive with Altair's hobbyist kit. Fully assembled, the 8080 is \$931. Unassembled, it's \$599.

The IMSAI 8080 is made for commercial users, and it looks it. Inside and out. The cabinet is attractive, heavy gauge aluminum. The heavy duty lucite front panel has an extra 8 program controlled LED's. It plugs directly into the Mother Board without a wire harness. And rugged commercial grade paddle switches are backed up by reliable debouncing circuits.

The system is optionally expandable to a substantial system with 22 slots in a single printed circuit board. And the durable card cage is made of commercial-grade anodized aluminum.

The IMSAI 8080 power supply produces a true 28 amp current, enough to power a full system. You can expand to a powerful system with 64K of software protectable memory plus an intelligent floppy disk controller. You can add an audio tape cassette input device, a printer plus a video terminal and a teletype. And these peripherals will function with an 8-level priority interrupt system. BASIC software is available in 4K, 8K and 12K.

Get a complete illustrated brochure describing the IMSAI 8080, options, peripherals, software, prices and specifications. Send one dollar to cover handling to IMS. The IMSAI 8080. From the same technology that developed the HYPERCUBE Computer architecture and Intelligent Disk systems.

Dealer inquiries invited.

#### **IMSAI**

Manufacturing Corp. 14860 Wicks Boulevard San Leandro, CA 94577 (415) 483-2093

Dept. RE-1

CIRCLE 40 ON FREE INFORMATION CARD

# KOMPUTER KORNER

#### PAUL E. FIELD, DAVID G. LARSEN, PETER R. RONY, and JONATHAN A. TITUS\*

THIS MONTH, WE RETURN TO THE SUBJECT OF the substitution of software for hardware, i.e., the substitution of machine-level routines and subroutines for specific digital hardware devices that store, manipulate, transmit, or receive digital information. The hardware device that we will discuss is the universal asynchronous receiver/transmitter, or UART-a 40-pin integrated circuit that contains an independent 8-bit asynchronous receiver and an independent 8-bit asynchronous transmitter. Data rates range from DC to 60,000 bits per second. The receiver and transmitter sections of the IC can be programmed for 5, 6, 7, or 8 data bits; 1 or 2 stop bits; even or odd parity; and parity or no parity. The IC contains a variety of flags.

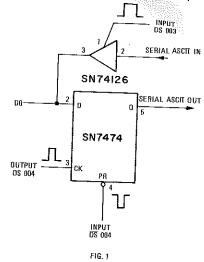

An interface circuit for a simplified soft-ware UART is shown in Fig. 1. Owing to the nature of the specific application that the circuit was designed for, there was no need for special flag-bits or error checking. Thus, the interface circuit consists of a single three-state input buffer gate (SN74126), a single output data-latch (SN7474), two input device-select pulses, and one output device-

select pulse. With appropriate modifications of the device select pulses, this circuit can be used with almost any microprocessor IC. In our case, an 8080A-based microcomputer

TABLE 1—MICROCOMPUTER SUBROUTINE that demonstrates the asynchronous serial transmission of an eleven-bit ASCII word at a teletype speed of 110 Baud.

| memory<br>address | Instruc-<br>tion byte | Mnemonic      | Description                                                                |

|-------------------|-----------------------|---------------|----------------------------------------------------------------------------|

| •                 | Accumula              | ator contains | 8-bit ASCH word Bit a con-                                                 |

|                   | set for ev            | en or odd p   | 8-bit ASCII word. Bit 8 is the parity bit that can be arity, or no parity. |

| 144               | 056                   | MVIL          | Set ASCII word bit counter to 013                                          |

| 145               | 013                   | 013           | ost noon word bit counter to 013                                           |

| 146               | 267                   | ORA A         | Set carry bit to logic 0                                                   |

| 147               | 027                   | RAL           | Rotate carry bit to DO in accumulator                                      |

| 150<br>151        | 323                   | TUO           | Output carry bit to SN7474 latch                                           |

| 152               | 004                   | 004           | 5 - 10 5 5 1 7 1 4 1 d(C)                                                  |

| 153               | 315                   | CALL          | Call 9.09 ms time-delay subroutine                                         |

| 154               | 'B2'<br>'B3'          | 'B2'          | LO address byte of time-delay subrouting                                   |

| 155               | 037                   | 'B3'          | in dudiess byte of time-delay subrouting                                   |

| 156               | 067                   | RAR<br>STC    | notate bit in ASCII word to DO in accumulate                               |

| 157               | 323                   | OUT           | oct carry bit to logic 1                                                   |

| 160               | 004                   | 004           | Output bit to SN7474 latch                                                 |

| 161               | 055                   | DCR L         | Decorporate Lil                                                            |

| 162               | 302                   | JNZ           | Decerement bit counter by 1                                                |

|                   |                       |               | If bit counter has a value of zero, ignore this                            |

|                   |                       |               | instruction. If all of the bits in the 11-bit ASCII                        |

| 400               |                       |               | word have not yet been transmitted, jump to address LO = 152 above.        |

| 163               | 152                   | 152           | LO address byte                                                            |

| 164               | ,B3,                  | 'B3'          | HI address but-                                                            |

| •                 | At this poin          | nt, the 8-bit | ASCII word contained to the                                                |

| •                 | been transr           | nitted. Two s | t at logic 0, here he added at the end of the eight                        |

|                   |                       |               | t, at logic 0, has been added at the beginning of                          |

| _                 | the eight bi          | 18.           | 99 07                                                                      |

\*This article is reprinted courtesy American Laboratories. Dr. Field and Mr. Larsen, Department of Chemistry, and Dr. Rony, Department of Chemical Engineering, are with the Virginia Polytechnic Institute & State University. Mr. Titus is president of Tychon, Inc. Dr. Field is guest author of this month's column.

operating at 750 kHz was used. This generates and detects, asynchronous serial ASCH-coded 5-volt TTL data. For teletype operation, additional hardware is required to convert the 5-volt logic levels to 20 mA current-loop operation.

continued on page 24

## 358 Ways To Save On Instruments. Citizens Band, Burglar Alarms, Automotive & Hobby **Electronics!**

The more you know about electronics, the more you'll appreciate EICO. We have a wide range of products for you to choose from, each designed to provide you with the most pleasure and quality performance for your money. The fact that more than 3 million EICO products are in use attests to their quality and performance.

#### "Build-it-Yourself" and save up to 50% with our famous electronic kits.

For latest EICO Catalog and name of nearest EICO Distributor, check reader service card or send 50¢ for fast first class mail service.

#### EICO-283 Malta Street. Brooklyn, N.Y. 11207

Leadership in creative electronics since 1945.

CIRCLE 38 ON FREE INFORMATION CARD

#### KOMPUTER KORNER

continued from page 22

#### Transmit subroutine

The transmit subroutine, shown in Table I, for the software UART occupies twenty to twenty-five successive program steps in memory once the appropriate PUSH, POP. and RET instructions have been included. Also required is a 9.09 ms time-delay subroutine that corresponds to an asynchronous serial ASCII data transmission rate of 110 Baud, i.e., teletype speed. The program in Table 1 can be described as follows:

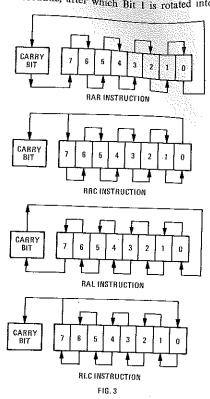

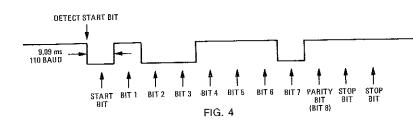

Register L is used as the bit counter for the 11-bit ASCII word, and is set initially to octal 013. The seven data-bits plus the parity bit, which is Bit 8, are assumed to be present in the accumulator. At the LO memory address 146, the accumulator is OR'ed to itself to clear the carry bit (shown on the far left in Fig. 2.) In Fig. 2, the least significant data bit

| ACCUMULATOR                |          |          |          |          |          |          |          |          |  |  |

|----------------------------|----------|----------|----------|----------|----------|----------|----------|----------|--|--|

| CARRY                      | 97       | D6       | D5       | D4       | Đ3       | D2       | D1       | DØ       |  |  |

| G                          | BIT<br>8 | BIT<br>7 | BIT<br>6 | BIT<br>5 | BIŢ<br>4 | BIT<br>3 | BIT<br>2 | BIT<br>1 |  |  |

| ROTATE LEFT ROTATE RIGHT - |          |          |          |          |          |          |          |          |  |  |

is Bit 1. At address LO = 147, a RAL instruction is performed to rotate the start bit to bit position DO in the accumulator, Fig. 3 should provide you with assistance in understanding the four different rotate instructions

MODEL 100A AUDIO RESPONSE PLOTTING SYSTEM and general purpose sweep/tone burst/pulse generator consists of two sine /square/triangle function generators, pulse generator, frequency counter and peak amplitude measurement sections. It is primarily intended to generate a frequency response plot on an X - Y recorder or scope.

Time base generator offers symmetrical or inde Time base generator orners symmetrical or independent control of the positive and negative sides of the ramp providing a duty cycle of .7% to 99.3%. Frequency range is .0035Hz to 100kHz. Amplitude is 15Vpp into 500  $\Omega$  with  $\pm$ 5VDC offset. The time base output drives the X axis of an X - Y recorder. Manual mode provided for setup.

Audio sweep generator provides manual frequency adjustment or log/linear sweep of 20Hz to 20kHz. Blanking mode produces zero reference line onn X · Y recorder or tone burst. Amplitude is 45 Vpp into 500  $\Omega$  or 10 Vpp into 8  $\Omega$ .

Pulse generator frequency range is .0035Hz to 525kHz. Pulse wideth is adjusted independent of frequency from 4 seconds to 40 nanoseconds. Outputs are complimentary TTL.

Peak amplitude measurement section measures internal or external signals from mike to power amp level. Amplitude output drives Y axis of X - Y recorder.

Frequency counter is 6 digit, line triggered, and reads either internal or external. Sensitivity is 50 mv peak at 20kHz.

Dimensions: 8 x 14 x 3. Shipping Weight 9 lbs. \$550, stock to 30 days. Warranty: 1 year. DELITY SOUND San Bernardino, Ca 92408 (714) 889-7823

CIRCLE 5 ON FREE INFORMATION CARD

in the 8080A microprocessor instruction set. At address LO = 150, the start bit is output to the SN7474 data latch. The program then goes into a 9.69 ms time-delay subroutine, after which Bit I is rotated into

the DO accumulator position and the carry bit is set to logic 1. Bit 1 is fed to the SN7474 latch, the ASCII word bit counter in register L is decremented and program control is returned to the time-delay subroutine that is called at address LO = 152. The loop from LO = 152 to LO = 164 is executed a total of eleven times, after which register L becomes zero and the JNZ instruction at address LO = 162 is ignored.

A software UART transmit subroutine possesses a flexibility equivalent to the original 40-pin UART chip. With appropriate modifications to the program or the original accumulator data, you can transmit 5, 6, 7, or 8 data bits; 1 or 2 stop bits; even or odd parity; and parity or no parity. The timedelay subroutine can be modified so that you can transmit at data rates from 60 to 9600 Baud for a 750-kHz clock rate and higher for 2-MHz and 4-MHz clock rates.

The conversion from one data transmission rate to another is easily accomplished with the aid of appropriate software time-delay subroutines that replace R-C time-constant circuits. An additional advantage that is gained from the use of software is the potential to perform code conversions. For example, 5-level Baudot KSR machines are in widespread use and can still be obtained for under \$50. It is not too difficult to develop software that converts ASCII to Baudot and thus produce an inexpensive hard-copy terminal for the laboratory scientist, engineer, ham or computer buff.

#### Receive subroutine

The software UART receive subroutine requires 50 instructions and will not be repeated here. (Copies of the transmit and receive subroutines and a description of the

smart data-entry station are available from Professor Paul Field, Department of Chemistry, Virginia Polytechnic Institute and State University, Blacksburg, VA 24061.) The basic programming concepts associated with the receive subroutine are shown in Fig. 4, which represents an 11-bit asynchronous serial ASCII word that is being detected by the 8080A-based microcomputer with the aid of the SN74126 three-state buffer gate shown in Fig. 1. The program repeatedly tests the serial ASCII input line for a logic 0 state. Once a logic 0 state is detected, which corresponds to a start bit, the program goes into a 4.54-ms wait loop. Upon leaving the wait loop, the program again inputs the logic 0 into bit position DO in the accumulator, thus testing the validity of the start bit. The start bit is rotated to the carry bit and the program then enters a 9.09-ms wait loop, after which it inputs Bit 1 into position DO in the accumulator. Register H is used as the SAVE register that stores the growing ASCII data word. The SAVE register is rotated one position, and the 9.09-ms wait loop is again entered, after which Bit 2 (a logic 0 in Fig. 4) is input into bit position DO in the accumulator. The input of successive data and parity bits continues until the entire 8-bit data word is entered into the SAVE register. The two stop bits are also detected. With appropriate modifications, the program can detect parity or framing errors or an overrun condition. A data-ready flag signal can also be generated from software with the aid of a second SN7474 latch.

#### TIMESHARE

continued from page 67

able A and the second value to B. Line 20 assigns to variable C the value of the square root of the sum of the two entered values to the third power. Line 30 outputs the value of C to the terminal. Line 40 transfers execution back to line 10, and you're ready to execute the problem for two new values.

When you have all the results you require, you push the ESC key (escape) to stop the program, then sign off or enter a new program.

Notice the similarity between BASIC and English:

- INPUT—to input a value for a variable

- LET-to let a variable equal a

- · PRINT-to print the results at the terminal · GOTO-to go to another part of

- the program.

This similarity exists throughout the BASIC language, which makes it ideal for people who are not computer programmers but need or desire to use a R-E computer.

#### **Applications**

The above software UART routines were used in a "smart" remote data-entry station that was tied via a 20 mA current-loop to a PDP 8/L minicomputer in a physical chemistry laboratory. The data entry station intercepted the 20-mA teletype current-loop tied to the minicomputer. The remote data-entry station permitted students to load data into memory and then transmit it as a block to the minicomputer, which analyzed the data and provided a print-out. With the 20-mA current loop operating in the full duplex mode, ten or more remote data-entry stations could be tied to the minicomputer.

This column provides a good demonstration of the software-hardware tradeoffs that can be accomplished using microcomputers. Similar, and perhaps more comprehensive, routines have already been written for all of the popular microprocessor chips, such as the 16-bit PACE or the 8-bit 6800. The faster and less expensive that microcomputers become, the more likely that all moderate speed digital functions will be executed via software. The theme of software replacing hardware is an important one, and we will return to it many times in future columns.

#### 8.192 x 8 BIT STATIC MEMORY

**EXCEPTIONALLY LOW POWER**

#### KIT \$29500

- ★ ALTAIR 8800 / IMSAI 8080 BUS COMPATIBLE ★ FAST 215 nS-FULL SPEED-FOR Z80 ALSO

- ★ EXCEPTIONALLY LOW POWER—LESS HEAT

- \* LESS THAN OTHER "LOW POWER" MEMORY

- ★ BATTERY STAND-BY CAPABILITY

- \* ALL SIGNALS TO MOS DEVICES BUFFERED

PROTOTYPING BOARD Z80-CPU CARD RACK 16K RAM 2K ROM/2K RAM LOW PROFILE IC SOCKETS **EDGE CONNECTORS DB25 CONNECTORS**

SHIPPING EXTRA, ADD \$2.00 NJ RES. ADD 5% SALES TAX

#### **ELECTRONIC CONTROL TECHNOLOGY** P.O. Box 6, Union, New Jersey 07083

CIRCLE 67 ON FREE INFORMATION CARD

### Fast, Fool-proof Alignment

**B&K-PRECISION**

#### SWEEP/MARKER GENERATOR

Model 415, \$485

With the B&K-PRECISION Model 415 you can complete a TV alignment in about the time you would spend hooking up the instruments for conventional alignment procedures. It's ideal for testing adjacent channel interference in CATV installations, too.

Everything you need is built into the Model 415—sweep and marker generators, a marker adder and three bias supplies. The 10 crystalcontrolled if markers can be shown either vertically or horizontally on your scope, and they light up on the front panel IF response and chroma bandpass diagrams as you use them.

Proper set alignment is assured and is almost automatic when you follow the Model 415's programmed alignment procedures.

Contact your local B&K-PRECI-SION distributor for a demonstration, or write for detailed information on how the Model 415 can save you time and increase your profits.

6460 West Cortland Avenue Chicago, Illinois 60635 • 312/889-9087 In Canada: Atlas Electronics, Ontario

CIRCLE 79 ON FREE INFORMATION CARD