# Virtuoso m

## The Virtual Single Processor Programming System

**User Manual**

Covers :

# Virtuoso Micro TM

# Virtuoso Classico TM

Version 3.11

Copyright 1996 Eonic Systems

## **Table of Contents**

| Introduction                     | INT - 1 |

|----------------------------------|---------|

| Release notes                    | INT - 3 |

| V.3.01 September 1992            | INT - 3 |

| V.3.05 January 1993              |         |

| V.3.09 September 1993            |         |

| V.3.09.1 November 1993           |         |

| V.3.11 September 1996            | INT - 4 |

| Implementation-Specific Features | INT - 5 |

| Trademark Notices                | INT - 6 |

| The history of Virtuoso          | INT - 7 |

| Milestones                       | INT - 8 |

| Manual Format                    | INT - 9 |

| License agreement                | LIC - 1 |

| OWNERSHIP AND CONDITIONS :       | LIC - 1 |

| 1. OWNERSHIP :                   | LIC - 1 |

| 2. FEES :                        | LIC - 1 |

| 4. CUSTOMER'S PRIVILEGES :       |         |

| 5. CUSTOMER OBLIGATIONS :        |         |

| 6. CUSTOMER PROHIBITIONS :       | LIC - 3 |

| 7. LIMITED WARRANTY :            | LIC - 4 |

| 8. GENERAL :                     | LIC - 4 |

### Part 1. The concepts

| Installation                            | P1 - 3  |

|-----------------------------------------|---------|

| Installing the software                 | P1 - 3  |

| Kernel libraries provided               |         |

| Confidence test                         | P1 - 4  |

| Virtuoso compilation symbols            | P1 - 5  |

| The license agreement                   | P1 - 6  |

| Site developers license and runtimes    | P1 - 6  |

| Support and maintenance                 | P1 - 6  |

| Cross development capability            |         |

| The final reference                     | P1 - 7  |

| A short introduction                    | P1 - 8  |

| The one page manual                     |         |

| Underlying assumptions when programming | P1 - 9  |

| Virtuoso : an overview                  | P1 - 10 |

| Requirements for a programming system   | P1 - 10 |

P1 - 1

| The high level view : a portable set of services              | . P1       | ۱ - | 10 |

|---------------------------------------------------------------|------------|-----|----|

| A multi-tasking real-time microkernel as the essential module | . P1       | -   | 10 |

| Classes of microkernel services                               | . P1       | - ا | 11 |

| The object as the unit of distribution                        | . P1       | -   | 11 |

| A multi-level approach for speed and flexibility              | . P1       | - ا | 13 |

| An execution trace illustrated                                | . P1       | I - | 16 |

| Processor specific support                                    | . P1       | -   | 17 |

| Functional support from Virtuoso                              | <b>P</b> 1 | -   | 18 |

| Introduction                                                  |            |     |    |

| Parallel processing : the next logical step                   | . P1       | -   | 18 |

| What is (hard) real-time ?                                    | . P1       | -   | 20 |

| The high demands of Digital Signal Processing                 | . P1       | -   | 21 |

| A first conclusion                                            | . P1       | -   | 22 |

| Parallel programming : the natural way                        | . P1       | -   | 22 |

| About objects and services                                    | . P1       | -   | 23 |

| The Virtuoso microkernel objects and the related services     | . P1       | -   | 23 |

| Class Task                                                    |            |     |    |

| The task as a unit of execution                               | . P1       | -   | 23 |

| Priority and scheduling                                       | . P1       | -   | 24 |

| Task execution management                                     | . P1       | -   | 25 |

| Class Timer                                                   | . P1       | -   | 26 |

| Class Memory                                                  | . P1       | -   | 27 |

| Class Resource                                                | . P1       | -   | 29 |

| Class Semaphore                                               | . P1       | -   | 29 |

| Class Message                                                 |            |     |    |

| Once-only synchronization : the KS_MoveData() service         | . P1       | -   | 32 |

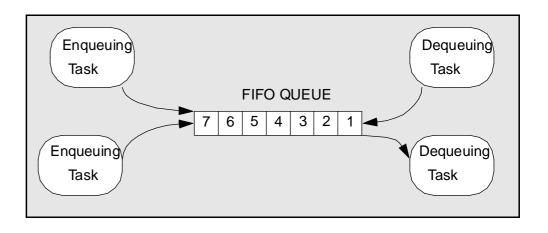

| Class Queue                                                   | . P1       | -   | 32 |

| Class Special                                                 | . P1       | -   | 33 |

| Class Processor Specific                                      | . P1       | -   | 33 |

| Low level support with Virtuoso                               | . P1       | -   | 34 |

| The ISR levels                                                |            |     |    |

| Levels supported by the Virtuoso products.                    | . P1       | -   | 37 |

| Support for parallel processing                               | . P1       | -   | 37 |

| Target Environment                                            |            |     |    |

| Virtuoso auxiliary development tools                          |            |     |    |

| Single processor operation                                    |            |     |    |

| Virtual Single Processor operation                            |            |     |    |

| Heterogeneous processor systems                               | . P1       | -   | 40 |

|                                                               | <b>P1</b>  |     |    |

| Hello, world                                                  |            |     |    |

| Use of a Queue                                                | . P1       | -   | 44 |

| Applications                                                  | 71         |     | 46 |

| Scalable embedded systems                                     |            |     |    |

| Complex control systems                                       | . P1       | -   | 47 |

| Simulation in the control loop | P1 - 47 |

|--------------------------------|---------|

| Fault tolerant systems         |         |

| Communication systems          | P1 - 48 |

### **PART 2: Reference Manual**

## **P2 - 1**

| Virtuoso microkernel types & data structures | P2 - 3  |

|----------------------------------------------|---------|

| Microkernel types                            | P2 - 3  |

| Tasks                                        | P2 - 3  |

| Task Identifier & Priority                   | P2 - 4  |

| Task group set                               | P2 - 4  |

| Task State                                   |         |

| Task Entry Point                             | P2 - 5  |

| Task Abort Handler                           | P2 - 5  |

| Task Stack                                   | P2 - 5  |

| Task Context                                 | P2 - 5  |

| Semaphores                                   | P2 - 5  |

| Mailboxes                                    | P2 - 6  |

| Queues                                       | P2 - 8  |

| Resources                                    | P2 - 8  |

| Timers                                       | P2 - 9  |

| Memory maps                                  | P2 - 10 |

| Virtuoso microkernel services                | P2 - 11 |

| Short overview                               | P2 - 11 |

| Important note                               | P2 - 11 |

| Task control microkernel services            |         |

| Semaphore microkernel services               | P2 - 13 |

| Mailbox microkernel services                 | P2 - 14 |

| Queue microkernel services                   | P2 - 15 |

| Timer management microkernel services        | P2 - 16 |

| Resource management microkernel services     | P2 - 17 |

| Memory management microkernel services       | P2 - 18 |

| Special microkernel services                 |         |

| Drivers and processor specific services      | P2 - 18 |

| Nanokernel types and datastructures          | P2 - 21 |

| Nanokernel processes and channels            | P2 - 21 |

| Nanokernel channels                          | P2 - 21 |

| Nanokernel services                          | P2 - 23 |

| Process management                           |         |

| ISR management                               |         |

| Semaphore based services                     |         |

| Stack based services                         |         |

| Linked list based services                   | P2 - 24 |

| Alphabetical List of Virtuoso microkernel services | P2 - 25 |

|----------------------------------------------------|---------|

| KS_Abort                                           | P2 - 26 |

| KS_AbortG                                          | P2 - 27 |

| KS_Aborted                                         | P2 - 28 |

| KS_Alloc                                           | P2 - 29 |

| KS_AllocW                                          | P2 - 30 |

| KS_AllocWT                                         | P2 - 31 |

| KS_AllocTimer                                      |         |

| KS_Dealloc                                         | P2 - 33 |

| KS_DeallocTimer                                    | P2 - 34 |

| KS_Dequeue                                         | P2 - 35 |

| KS_DequeueW                                        | P2 - 36 |

| KS_DequeueWT                                       | P2 - 37 |

| KS_DisableISR                                      | P2 - 39 |

| KS_Elapse                                          | P2 - 40 |

| KS_EnableISR                                       | P2 - 41 |

| KS_Enqueue                                         | P2 - 42 |

| KS_EnqueueW                                        | P2 - 44 |

| KS_EnqueueWT                                       | P2 - 46 |

| KS_EventW                                          | P2 - 48 |

| KS_GroupId                                         | P2 - 49 |

| KS_HighTimer                                       | P2 - 50 |

| KS_InqMap                                          | P2 - 51 |

| KS_InqQueue                                        | P2 - 52 |

| KS_InqSema                                         | P2 - 53 |

| KS_JoinG                                           | P2 - 54 |

| KS_LeaveG                                          | P2 - 55 |

| KS_Linkin                                          |         |

| KS_LinkinW                                         |         |

| KS_LinkinWT                                        | P2 - 59 |

| KS_Linkout                                         |         |

| KS_LinkoutW                                        |         |

| KS_LinkoutWT                                       |         |

| KS_Lock                                            | P2 - 65 |

| KS_LockW                                           |         |

| KS_LockWT                                          |         |

| KS_LowTimer                                        |         |

| KS_MoveData                                        |         |

| KS_Nop                                             |         |

| KS_Nodeld                                          |         |

| KS_PurgeQueue                                      |         |

| KS_Receive                                         |         |

| KS_ReceiveData                                     |         |

| KS_ReceiveW                                        |         |

| KS_ReceiveWT                                       | P2 - 79 |

| KS_F         | ResetSema                              | P2            | - 81 |

|--------------|----------------------------------------|---------------|------|

| KS_F         | ResetSemaM                             | P2            | - 82 |

| KS_F         | RestartTimer                           | P2            | - 83 |

|              | Resume                                 |               |      |

| KS_F         | ResumeG                                | P2            | - 85 |

| KS_S         | Send                                   | P2            | - 86 |

|              | SendW                                  |               |      |

| KS_S         | SendWT                                 | P2            | - 89 |

| KS_S         | SetEntry                               | P2            | - 91 |

| KS_S         | SetPrio                                | P2            | - 92 |

| KS_S         | SetSlice                               | P2            | - 93 |

| KS_S         | SetWlper                               | P2            | - 94 |

| KS_S         | Signal                                 | P2            | - 95 |

| KS_S         | SignalM                                | P2            | - 96 |

| KS_S         | Sleep                                  | P2            | - 97 |

| KS_S         | Start                                  | P2            | - 98 |

|              | StartG                                 |               |      |

|              | StartTimer                             |               |      |

| KS_S         | StopTimer                              | P2 -          | 101  |

|              | Suspend                                |               |      |

| KS_S         | SuspendG                               | P2 -          | 103  |

| KS_T         | askld                                  | P2 -          | 104  |

| KS_T         | askPrio                                | P2 -          | 105  |

| KS_T         | est                                    | P2 -          | 106  |

| KS_T         | estMW                                  | P2 -          | 107  |

| KS_T         | estMWT                                 | P2 -          | 108  |

| KS_T         | estW                                   | P2 -          | 110  |

| KS_T         | estWT                                  | P2 -          | 111  |

| KS_L         | Jnlock                                 | P2 -          | 112  |

| KS_L         | Jser                                   | P2 -          | 113  |

| KS_V         | Vait                                   | P2 -          | 114  |

| KS_V         | VaitM                                  | P2 -          | 115  |

| KS_V         | VaitMT                                 | P2 -          | 116  |

|              | VaitT                                  |               |      |

| KS_V         | Vorkload                               | P2 -          | 119  |

| KS_Y         | /ield                                  | P2 -          | 120  |

| Hostserver a | and netloader                          | <b>P2 -</b> 1 | 121  |

|              | r functionality                        |               |      |

|              | tting and booting the target           |               |      |

|              | e                                      |               |      |

| Host         | interface definition.                  | P2 -          | 122  |

|              | f boards                               |               |      |

|              | f nodes.                               |               |      |

|              | node definition.                       |               |      |

|              | f comport links available for booting. |               |      |

|              | · ···································· | ··· -         |      |

| Host server interface                                | P2 - 125                         |

|------------------------------------------------------|----------------------------------|

| Host interface low level driver                      |                                  |

| Higher level drivers                                 |                                  |

| Console input and output                             |                                  |

| Standard I/O driver                                  |                                  |

| Graphics driver                                      |                                  |

| Runtime libraries                                    | P2 - 128                         |

| Standard I/O functions                               | P2 - 128                         |

| Implementation limits                                | P2 - 128                         |

| Standard I/O functions                               | P2 - 128                         |

| PC graphics I/O                                      | P2 - 131                         |

| Overview                                             | P2 - 131                         |

| Driver and mode selection                            | P2 - 132                         |

| Read or write graphics parameters and context        | P2 - 134                         |

| Drawing pixels and lines                             | P2 - 136                         |

| Drawing filled forms                                 |                                  |

| Text plotting                                        | P2 - 139                         |

| Other graphical calls                                |                                  |

| System Configuration                                 | P2 - 141                         |

| System configuration concepts                        |                                  |

| Kernel objects                                       |                                  |

| Sysdef : system definition file format               |                                  |

| Description requirements for the kernel object types |                                  |

| Node description                                     |                                  |

| Driver description                                   |                                  |

| Link descriptions                                    |                                  |

| The routing tables                                   |                                  |

| Task definitions                                     |                                  |

| Semaphore definitions                                | P2 - 150                         |

| Resource definitions                                 | P2 - 150                         |

| Queue definitions                                    | P2 - 150                         |

| Mailbox definitions                                  | P2 - 151                         |

| Memory map definitions                               | P2 - 151                         |

| Note on the size parameters                          | P2 - 151                         |

| Other system information and system initialization   | P2 - 152                         |

| Debugging environment under Virtuoso                 | P2 - 154                         |

| Task level debugger concepts                         | P2 - 154                         |

| Entry into the debugger                              | P2 - 154                         |

| Invoking the debugger from the keyboard              |                                  |

| Invoking the debugger from within your program       |                                  |

| Differences at system generation time                |                                  |

|                                                      |                                  |

| Debugger commands                                    | P2 - 155                         |

| Debugger commands<br>Tasks<br>Queues                 | P2 - 155<br>P2 - 156<br>P2 - 156 |

| Semaphores                                                     | P2 - 158 |

|----------------------------------------------------------------|----------|

| Resources                                                      |          |

| Memory Partitions                                              |          |

| Tracing monitor                                                | P2 - 160 |

| Mailboxes                                                      |          |

| Network buffers                                                | P2 - 164 |

| Clock/Timers                                                   | P2 - 164 |

| Stack Limits                                                   | P2 - 165 |

| Zero Queue/Map/Resource Statistics                             | P2 - 165 |

| Other processor                                                |          |

| Task Manager                                                   |          |

| Suspend                                                        |          |

| Resume                                                         |          |

| Abort                                                          | P2 - 167 |

| Start                                                          | P2 - 167 |

| Exit \$TLDEBUG                                                 | P2 - 167 |

| Exit TLDEBUG                                                   | P2 - 167 |

| Help                                                           | P2 - 167 |

| The Workload Monitor                                           | P2 - 168 |

| Practical hints for correct use                                | P2 - 170 |

| Flexible use of the messages                                   |          |

| General features                                               |          |

| Mailboxes                                                      |          |

| Using messages                                                 |          |

| On the abuse of semaphores                                     |          |

| On using the single processor versions for multiple processors |          |

| Hints on system configuration                                  |          |

| Customized versions and projects                               |          |

| Microkernel C++ interface                                      | P2 - 177 |

|                                                                |          |

| Microkernel C++ classes                                        |          |

| Kernel object generation by sysgen<br>KTask                    |          |

| KActiveTask                                                    |          |

| KTaskGroup                                                     |          |

| KSemaphore                                                     |          |

| KMailBox                                                       |          |

| KMessage                                                       |          |

| KQueue                                                         |          |

| KMemoryMap                                                     |          |

| KResource                                                      |          |

| KTimer                                                         |          |

| A sample C++ application                                       |          |

| Sysgen generated files                                         |          |

| Changes to the program files                                   |          |

| Traps and Pitfalls of C++                                      |          |

|                                                                | EZ = 197 |

| art 3: Binding Manual                                    | P3 - 1   |

|----------------------------------------------------------|----------|

| Virtuoso on the Analog Devices 21020 DSP                 | ADI - 1  |

| Virtuoso implementations on the 21020                    |          |

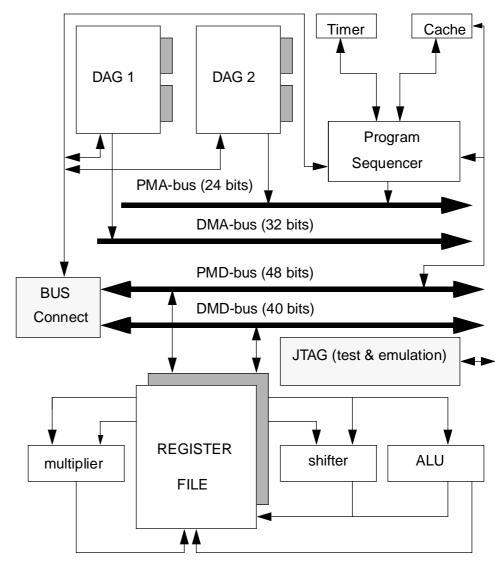

| DSP-21020 chip architecture                              |          |

| ADSP-21020 addressing modes                              |          |

| Special purpose registers on the ADSP-21020              |          |

| MODE1-register and MODE2-register                        |          |

| Arithmetic status register (ASTAT)                       |          |

| Sticky arithmetic status register (STKY)                 |          |

| Interrupt latch (IRPTL) and Interrupt Mask (IMASK)       |          |

| Program memory / Data memory interface control registers |          |

| PC stack (PCSTK) and PC stack pointer (PCSTKP)           |          |

| Status Stack                                             |          |

| USTAT                                                    |          |

| Relevant documentation                                   |          |

| Version of the compiler                                  |          |

| Runtime Environment                                      |          |

| Data types                                               |          |

| The Architecture file                                    |          |

| Runtime header (interrupt table)                         |          |

| Assembly language interface                              |          |

| Developing ISR routines on the 21020                     |          |

| Installing an ISR routine                                |          |

| Writing an ISR routine                                   |          |

| Alphabetical list of ISR related services                |          |

| The nanokernel on the 21020                              |          |

| Introduction                                             |          |

| Internal data structures                                 |          |

| Process managment.                                       |          |

| Nanokernel communications                                |          |

| C_CHAN - counting channel                                |          |

| L_CHAN - List channel                                    |          |

| S_CHAN - Stack channel                                   |          |

| REGISTER CONVENTIONS                                     |          |

| Interrupt handling                                       |          |

| The ISR-level                                            |          |

| Communicating with the microkernel                       |          |

| Virtuoso drivers on the 21020                            |          |

| Alphabetical List of nanokernel entry points             | ADI - 30 |

| _init_process                                            | ADI - 31 |

| start_process                                            |          |

| ENDISR1                                                  |          |

| K_taskcall                                               |          |

| KS_DisableISR()                                          |          |

| KS_EnableISR                                 | ADI - 37 |

|----------------------------------------------|----------|

| PRHI_GET                                     | ADI - 38 |

| PRHI_GETW                                    | ADI - 39 |

| PRHI_POP                                     |          |

| PRHI_POPW                                    | ADI - 41 |

| PRHI_PUT                                     | ADI - 42 |

| PRHI_PSH                                     | ADI - 43 |

| PRHI_SIG                                     | ADI - 44 |

| PRHI_WAIT                                    |          |

| PRLO_PSH                                     | ADI - 46 |

| YIELD                                        | ADI - 47 |

| Predefined drivers                           | ADI - 48 |

| The timer device driver                      | ADI - 48 |

| The host interface device driver             | ADI - 49 |

| Shared memory driver                         | ADI - 50 |

| Task Level Timings                           | ADI - 50 |

| Application development hints.               | ADI - 51 |

| Virtuoso on the ADSP 2106x SHARC             | ADI - 1  |

| Virtuoso implementations on the 21060        | ADI - 1  |

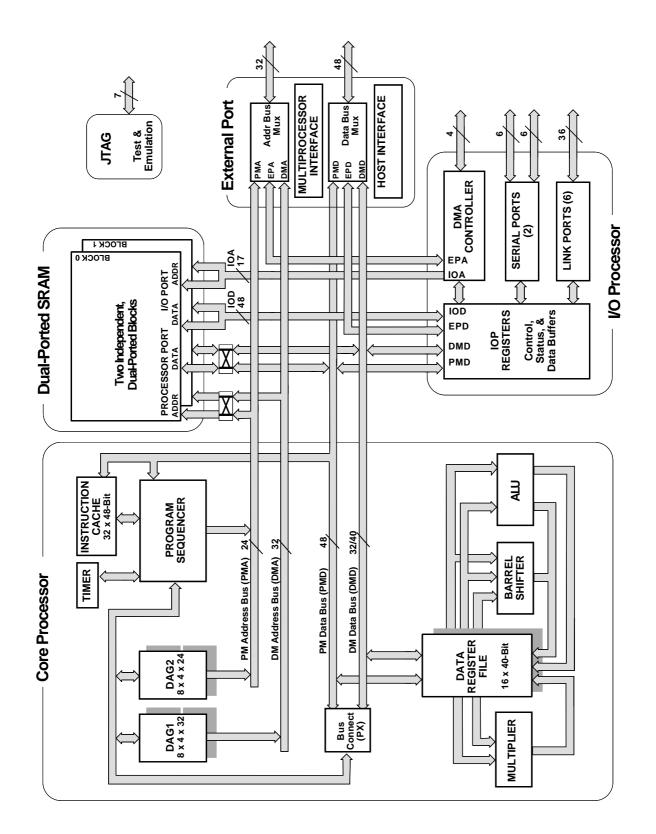

| SHARC chip architecture                      | ADI - 1  |

| Relevant documentation                       | ADI - 1  |

| Version of the compiler                      |          |

| SHARC silicon revisions                      |          |

| Developing ISR routines on the SHARC         |          |

| General principles                           |          |

| Writing an ISR routine                       |          |

| Installing an ISR routine                    |          |

| List of ISR related services                 |          |

| The nanokernel on the 21060                  |          |

| Introduction                                 |          |

| Internal data structures                     |          |

| Process management.                          |          |

| Nanokernel communications                    |          |

| SEMA_CHAN - counting or semaphore channel    |          |

| LIFO_CHAN - List channel                     |          |

| STACK_CHAN - Stack channel                   |          |

| Register conventions                         |          |

| Interrupt handling                           |          |

| The ISR-level                                |          |

| Communicating with the microkernel           |          |

| Additional microkernel features on the 21060 |          |

| Use of the PC stack and the counter stack    |          |

|                                              | ADI - 18 |

| Alphabetical List of nanokernel entry points | ADI - 19 |

|----------------------------------------------|----------|

| start_process                                | ADI - 20 |

| ENDISR1                                      | ADI - 21 |

| K_taskcall                                   |          |

| KS_DisableISR                                |          |

| KS_EnableISR                                 | ADI - 24 |

| PRHI_GET                                     |          |

| PRHI_GETW                                    |          |

| PRHI_POP                                     |          |

| PRHI_POPW                                    |          |

| PRHI_PUT                                     |          |

| PRHI_PSH                                     |          |

| PRHI_SIG                                     |          |

| PRHI_WAIT                                    |          |

| PRLO_PSH                                     |          |

| YIELD                                        |          |

| Predefined drivers                           | ADI - 35 |

| Virtuoso drivers on the 21060                |          |

| The timer device driver                      |          |

| The host interface device driver             |          |

| Netlink drivers                              |          |

| Raw Link drivers                             |          |

| Common remark for all link drivers           |          |

| Task Level Timings                           | ADI - 40 |

| Application development hints.               | ADI - 42 |

| Virtuoso on the Intel 80x86                  | l1 - 1   |

| Notes over PC interrupt drivers              |          |

| Warning when using Virtuoso on a PC          |          |

| Virtuoso on the Motorola 56K DSP             | M1 - 1   |

| Virtuoso versions on 56K                     | M1 - 1   |

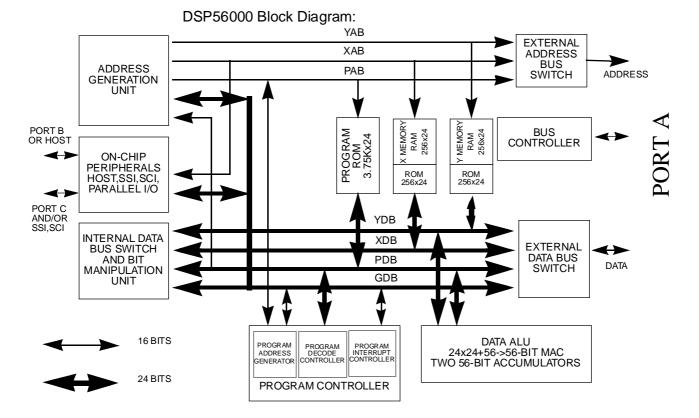

| DSP 56001 Chip Architecture                  |          |

| DSP56001 software architecture               |          |

| Addressing Modes                             |          |

| I/O Memory                                   |          |

| PORT A                                       |          |

| PORT B                                       |          |

| PORT C                                       |          |

| Exceptions                                   |          |

| Relevant documentation                       |          |

| C calling conventions and use of registers   |          |

| Storage Allocation                           |          |

| Register Usage                               |          |

| Subroutine Linkage                           | M1 - 11  |

| Preserved Registers                                              | M1 - 11 |

|------------------------------------------------------------------|---------|

| Register Return Values                                           | M1 - 11 |

| Parameter Passing                                                | M1 - 11 |

| Subroutine Call sequence                                         | M1 - 11 |

| Procedure Prologue and Epilogue                                  | M1 - 12 |

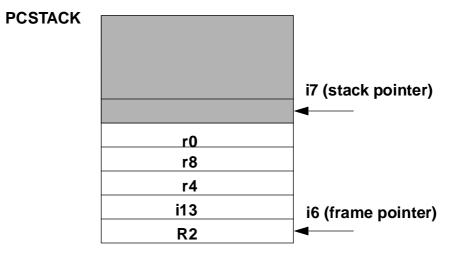

| Stack Layout                                                     | M1 - 13 |

| Interrupt Service Routines (ISR)                                 |         |

| ISR Conventions                                                  |         |

| Alphabetical list of ISR related services                        | M1 - 18 |

| Developing ISR routines                                          |         |

| The nanokernel on the 56002                                      |         |

| Predefined drivers                                               |         |

| The timer device driver                                          |         |

| The host interface device driver                                 | M1 - 24 |

| Task Level Timings                                               |         |

| Application development hints.                                   | M1 - 26 |

| Virtuoso on the Motorola 68030 systems                           | M2 - 1  |

| Source files of the Virtuoso kernel                              | M2 - 1  |

| Building an application executable                               | M2 - 2  |

| Configuration of the processor boards CC-112 of CompControl      | M2 - 3  |

| Additional information about the modules                         |         |

| Server program for CompControl VME system board, running on OS-9 | M2 - 9  |

| Purpose of the server program                                    |         |

| Source files for the server program                              |         |

| Use of the server program                                        | M2 - 11 |

| Virtuoso on the Motorola 96K DSP                                 | M3 - 1  |

| Virtuoso versions on 96K                                         | M3 - 1  |

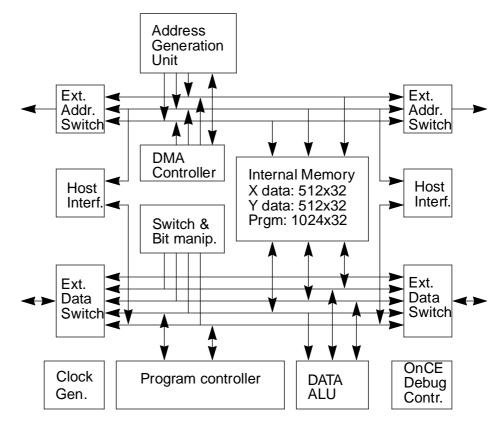

| DSP 96002 chip architecture                                      | M3 - 1  |

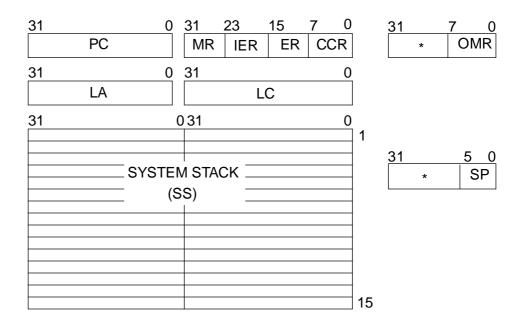

| DSP 96002 software architecture                                  | M3 - 3  |

| DSP 96002 addressing modes                                       | M3 - 7  |

| I/O memory and special registers                                 | M3 - 8  |

| Expansion ports control                                          | M3 - 8  |

| Exceptions                                                       |         |

| Relevant documentation                                           |         |

| C calling conventions and use of registers                       |         |

| Storage Allocation                                               |         |

| Segmentation model                                               |         |

| Register usage                                                   |         |

| Subroutine linkage                                               |         |

| Stack layout                                                     |         |

| Interrupt Service Routines (ISR)                                 |         |

| ISR conventions                                                  |         |

| Alphabetical list of ISR related services                        |         |

| The Nanokernel<br>Developing ISR routines                        |         |

|                                                                  |         |

| The nanokernel on the 96002                                               | M3 - 24 |

|---------------------------------------------------------------------------|---------|

| Predefined drivers                                                        | M3 - 24 |

| The timer device driver                                                   | M3 - 25 |

| The host interface device driver                                          | M3 - 25 |

| Task Level Timings                                                        |         |

| Application development hints.                                            | M3 - 27 |

| Virtuoso on the Motorola 68HC11.                                          | M4 - 1  |

| Virtuoso on the Motorola 68HC16 microcontroller.                          | M5 - 1  |

| Virtuoso on the Mips R3000 systems.                                       | R1 - 1  |

| Virtuoso on the INMOS T2xx, T4xx, T8xx.                                   | T8 - 1  |

| Introduction                                                              |         |

| The transputer : an example component for distributed processing          |         |

| Process control with transputers                                          |         |

| A solution based on process priority                                      |         |

| Modifying the FIFO scheduler on the transputer                            | T8 - 4  |

| The Virtuoso implementation                                               |         |

| Requirements for embedded real-time systems                               | T8 - 6  |

| Small grain versus coarse grain parallelism                               |         |

| Additional benefits from Virtuoso on the transputer                       |         |

| Device drivers with Virtuoso on the INMOS transputer                      |         |

| Performance results                                                       |         |

| Single processor version. (v.3.0.)                                        |         |

| The distributed version                                                   |         |

| Using the compiler libraries with Virtuoso                                |         |

| Specific Parallel C routines not to be used by the tasks                  |         |

| Specific routines of the INMOS C Toolset not to be used by the tasks      |         |

| Specific routines of the Logical Systems compiler not to be used by the t |         |

| Virtuoso on the INMOS T9000 transputer                                    | T9 - 1  |

| Virtuoso on the Texas Instruments TMS320C30 & C31                         | TI1 - 1 |

| Virtuoso versions on TMS320C30/C31                                        |         |

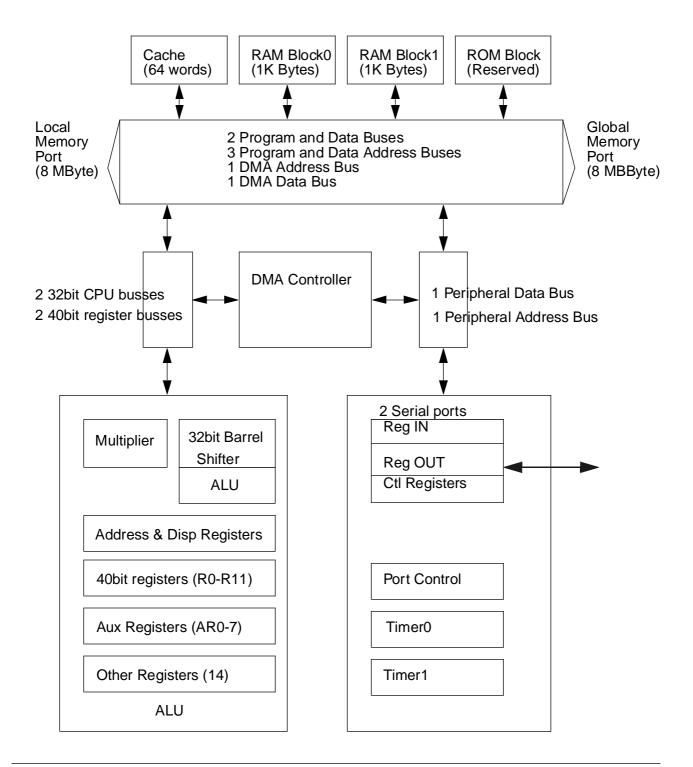

| TMS320C30 Chip Architecture                                               |         |

| TMS320C30 Software Architecture                                           |         |

| Addressing Modes                                                          |         |

| Relevant documentation                                                    |         |

| Application development hints                                             |         |

| Interrupt handlers and device drivers for Virtuoso on the TMS320C3x       |         |

| Interrupt handling in Virtuoso.                                           |         |

| Parts of a device driver.                                                 |         |

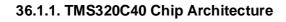

| Virtuoso on the Texas Instruments TMS320C40                               | TI2 - 1 |

| Brief description of the processor architecture                           |         |

| TMS320C40 Chip Architecture                                               |         |

| TMS320C40 Software Architecture                                           | Tl2 - 3 |

| Addressing Modes<br>Relevant documentation<br>Programming in C and assembly<br>Data representation<br>Big and Small Models<br>Parameter passing conventions<br>Memory sections for the C compiler and Virtuoso<br><b>Programming the nanokernel</b> |          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                                                                                                                                                                                     | -        |

| Internal data structures                                                                                                                                                                                                                            |          |

| Process management.                                                                                                                                                                                                                                 |          |

| Nanokernel communications                                                                                                                                                                                                                           |          |

| C_CHAN - Counting channel                                                                                                                                                                                                                           |          |

| L_CHAN - List channel                                                                                                                                                                                                                               |          |

| S_CHAN - Stack channel                                                                                                                                                                                                                              |          |

| Register conventions                                                                                                                                                                                                                                |          |

| Interrupt handling                                                                                                                                                                                                                                  |          |

| Communicating with the microkernel                                                                                                                                                                                                                  |          |

| Virtuoso drivers on TMS320C40                                                                                                                                                                                                                       |          |

| Alphabetical List of nanokernel entry points                                                                                                                                                                                                        | TI2 - 22 |

| _init_process                                                                                                                                                                                                                                       | TI2 - 23 |

|                                                                                                                                                                                                                                                     | TI2 - 24 |

| ENDISR0                                                                                                                                                                                                                                             | TI2 - 25 |

| ENDISR1                                                                                                                                                                                                                                             | TI2 - 27 |

| K_taskcall                                                                                                                                                                                                                                          | Tl2 - 29 |

| KS_DisableISR()                                                                                                                                                                                                                                     | TI2 - 30 |

| KS_EnableISR                                                                                                                                                                                                                                        | Tl2 - 31 |

| PRHI_GET                                                                                                                                                                                                                                            | Tl2 - 32 |

| PRHI_GETW                                                                                                                                                                                                                                           | Tl2 - 33 |

| PRHI_POP                                                                                                                                                                                                                                            |          |

| PRHI_POPW                                                                                                                                                                                                                                           |          |

| PRHI_PUT                                                                                                                                                                                                                                            | TI2 - 36 |

| PRHI_PSH                                                                                                                                                                                                                                            |          |

| PRHI_SIG                                                                                                                                                                                                                                            |          |

| PRHI_WAIT                                                                                                                                                                                                                                           |          |

| PRLO_PSH                                                                                                                                                                                                                                            |          |

| SETISR1                                                                                                                                                                                                                                             |          |

| SYSDIS                                                                                                                                                                                                                                              |          |

| SYSENA                                                                                                                                                                                                                                              |          |

| SYSVEC                                                                                                                                                                                                                                              |          |

| YIELD                                                                                                                                                                                                                                               |          |

| Predefined drivers                                                                                                                                                                                                                                  | TI2 - 48 |

| The timer device drivers                                                                                                                                                                                                                            |          |

| Host interface device drivers                                                                                                                                                                                                                       | TI2 - 48 |

| Netlink drivers    | TI2 - 49 |

|--------------------|----------|

| Raw link drivers   | TI2 - 49 |

| Task Level Timings | TI2 - 50 |

## Glossary

# GLO - 1

## Index

### IX - 1

### Introduction

**Virtuoso**<sup>TM</sup> is a family of real-time processing programing systems. As this family is expanding it became necessary to differentiate between the different product offerings. The general philosophy however is the same: ease of use and portability with no compromize on the performance.

Most of the products are available in three different implementations.

**SP** : Single Processor implementation.

These implementations do not assume the presence of any other processor in the system. The Virtuoso kernel provides multi-tasking with preemptive scheduling.

MP : Single Processor implementation with multi-processor extensions.

The multi-processor extensions enable fast and easy interprocessor communication, all in about 500 instructions. With minimum set-up times, it provides for maximum performance by using the DMA engines when available. Communication is point-to-point between directly connected processors.

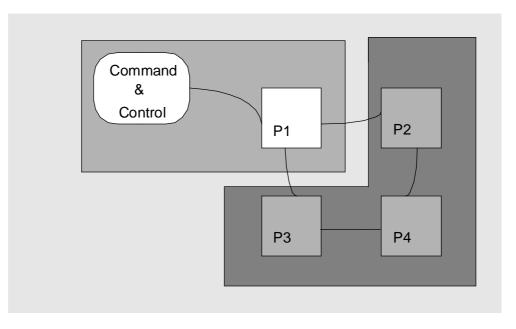

**VSP** : Virtual Single Processor implementation.

The true solution for parallel processing is to implement the communication as part of the kernel service, hence providing fully transparent parallel processing. The VSP implementation provides this feature by way of fully distributed semantics, permitting to move kernel objects and/or changes to the target topology without any changes to the source code.

The current product offerings are as follows :

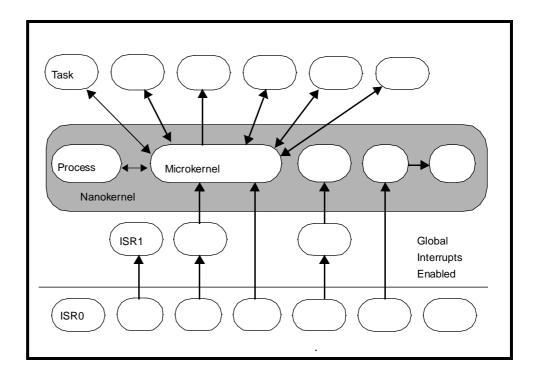

*Virtuoso Nano* is based on the core nanokernel of the Virtuoso product range. It can be very small (200 instructions) but is ultrafast. It provides for true multitasking and interprocess communication services. The VSP implementation is still not larger than 1000 instructions.

*Virtuoso Micro* features a small but fast microkernel that provides preemptive scheduling for a number of prioritized tasks. Well suited when preemptive scheduling is needed and the appication has moderate interrupt requirements..

*Virtuoso Classico* : a tight integration of Virtuoso's nanokernel and Virtuoso's microkernel. The microkernel provides fully distributed high level semantics with no source code changes when kerrnel objects or user tasks or moved in a processor network or when the system topology is changed.

*Virtuoso Modulo 0 to VI* contain a complete range of libraries in optimized assembly covering vector and matrix functions, filters, FFT, EISPACK (eigen value functions), BLAS (Basic Linear Algebra Subroutines, and 2-dimensional image processing. All written in optimized assembly. Part of the libraries were developed by Sinectoanalysis from Boston, MA and adapted for Virtuoso. The package is complemented by a board specific host server that boots the target network and provides standard I/O, PC graphics and heap allocation functions.

For the rest of the manual, we will often use the term Virtuoso as the context makes it clear what product offering is being discussed.

Virtuoso currently supports the following processors :

ARM, INMOS T2xx,T4xx, T8xx, T9000, TEXAS INSTRUMENTS TMS320C30/C31/C40, Motorola 68xxx, 68HC11, 68HC16, Intel 80x86 (real mode), MIPS R3000, Motorola 96K, 56K, Analog Devices 21020, 2106x, Pine & OakDSPCore. (contact Eonic Systems or your distributor for a list).

Not all processors supported by Virtuoso are supported with all possible implementations. A choice was made depending on the specific processor architecture as well as on the typical use made of the processor. In all cases is the microkernel available offering an identical interface from single 8bit microcontrollers to mixed parallel processing networks of 32bit DSPs and other processors.

As not all processor versions are fully upgraded to the latest version. Refer to the release floppy or the previous manual if there is a inconsistency. Eonic Systems is upgrading all versions to be source level compatible as much as possible.

Eonic Systems International Inc. has taken up the challenge to continually improve its product by further streamlining the code, by extending the functionality and the flexibility of the kernel and by adding tools that will support the designer during the development phase as well as during the rest of the life cycle of the applications developed. Therefore, the current version is subject to modification and will be upgraded on a regular base.

For more information : info@eonic.com

For support, contact : support@eonic.com

WEB page : http://www.eonic.com

### **Release notes**

#### V.3.01 September 1992

This version does not contain many changes. In particular :

- 1. The I/O library was revised and extended;

- **2.** Terminal type I/O is now a separate library;

- **3.** The compile and development cycle has been shortened by streamlining the makefiles and library decomposition;

- The KS\_Alloc kernel service was modified to allow deallocation when a task is aborted;

- 5. A new universal network loader.

We made a lot of efforts to support even better DSP applications. In particular :

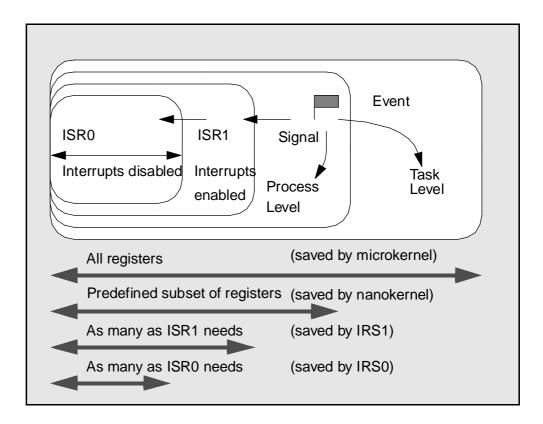

- 1. The ISR structure has been reviewed permitting to eliminate most of the interrupt disabling times.

- 2. Light context tasks were introduced. These are used internally by the kernel but can be defined and programmed as well by the user.

#### V.3.05 January 1993

The major novelty is the introduction of the nanokernel for the distributed version. This consists of several light context tasks and enables very fast interrupt servicing.

Following enhancements were added :

- 1. The router will use multiple paths, if possible.

- 2. A new service, the KS\_MoveData was introduced

- **3.** The transputer and C40 version can be used transparently on mixed networks.

- **4.** Introduction of an Application Development Support Package consisting of a Vector, Matrix and Flter library (separate product).

#### V.3.09 September 1993

The major change is the updating of the manual documenting the nanokernel. For the single processor versions, the same hostserver and netloader is being used as with the multiprocessor versions to improve the portability of the applications. Following changes were made :

- 1. An improved \*.NLI file format;

- 2. An improved tracing monitor.

#### V.3.09.1 November 1993

In this release all nanokernel services were implemented as traps. This has the benefit that the total interrupt disabling time was reduced and that the nanokernel code can be placed on any memory bank in relation to the program code.

The manual was largely updated and covers the Virtuoso support packages in a single manual. Virtuoso Nano is not yet documented in its VSP implementation

From this release on, every license includes free of charge a binary version of Virtuoso Micro for use with Borland C under DOS, permitting an easy cross development at the microkernel level.

#### V.3.11 September 1996

This release adds a C++ API to the microkernel services.

This reference part of this manual has been extensively revised,.

This version is the first version of Virtuoso to be tested production versions of the Analog Devices 2106x processor.

### **Implementation-Specific Features**

As these manuals are generic, not all the software versions will correspond fully with it. Some advanced features might be missing or implemented differently depending on the actual target processor. Note however that later versions are always supersets of the previous ones unless serious technical reasons dictated syntax changes. Refer to your interface libraries for a correct definition of the syntax and the read.me files.

Eonic Systems International makes no warranty, expressed or implied, with regard to this material including but not limited to merchantability or fitness for a given purpose. The information in this document is subject to change without notice. Eonic Systems International assumes no responsibility for any errors which may appear herein. Eonic Systems International shall have no liability for compensatory, special, incidental, consequential, or exemplary damages.

This document may not be copied in whole or in part without the express written permission of Eonic Systems International. The products described in this document are and shall remain the property of Eonic Systems International. Any unauthorized use, duplication, or disclosure is strictly forbidden.

### **Trademark Notices**

Virtuoso<sup>™</sup> is a trademark of Eonic Systems Inc. 12210 Plum Orchard Drive, Silver Spring, MD 20904 Tel. (301) 572 5000, Fax. (301) 572 5005 e-mail: info@eonic.com. For support : support@eonic.com WEB : http://www.eonic.com Europe : Nieuwlandlaan9, B-3200 Aarschot, Belgium. Tel. : (32) 16.62 15 85. Fax : (32) 16.62 15 84 Copyright © 1996 Eonic Systems, Inc.

*Virtuoso Nano* <sup>TM</sup> is a trademark of Eonic Systems Inc. *Virtuoso Micro* <sup>TM</sup> is a trademark of Eonic Systems Inc. *Virtuoso Classico* <sup>TM</sup> is a trademark of Eonic Systems Inc. *Virtuoso Modulo* <sup>TM</sup> is a trademark of Eonic Systems Inc. *Virtuoso Molto* <sup>TM</sup> is a trademark of Eonic Systems Inc.

RTXC is a trademark of A.T. Barrett & Associates. TRANS-RTXC is a trademark of Eonic Systems Inc. RTXC/MP is a trademark of Eonic Systems Inc. RTXCmon is a trademark of Eonic Systems Inc.

### The history of Virtuoso

Welcome to the world of **Virtuoso**. We think that you have purchased one of the most versatile and unique systems available for the implementation of a real-time system, be it on a single or on a multi-processor target system. Before we jump into the details, we would like to spend a few moments to explain the philosophy behind **Virtuoso**.

In 1989, Intelligent Systems International (which later became Eonic Systems), was founded. At that time, the INMOS transputer was the only processor available with in-built support for parallel processing, however, it lacked the ability to support tasks with multiple levels of priority. In order to apply this technology to hard real-time applications, ISI wrote a multi-tasking kernel for the transputer. Derived from RTXC, ISI added support for multiple processors, and launched a product called TRANS-RTXC.

In addition, ISI started to port to a variety of other processors. This was possible because TRANS-RTXC was redesigned much more with portability in mind, and re-named as RTXC/MP. It was available for targets ranging from 8bit microcontrollers to 32-bit multi-processor networks.

A major addition to the supported target processors was the Texas Instruments TMS320C30 and C40. This brought RTXC/MP into the DSP world, and to a new level of performance. However, the requirements of DSP applications needed a radical new approach in the implementation of the kernel. On the one hand, DSP applications running on hundreds of processors require a powerful and easily understood paradigm for distributed processing; while on the other hand the need to process interrupts from many sources requires an efficient, low-level approach. Often these apparently conflicting requirements are present in the same system.

The result of these considerations was **Virtuoso**. The concepts behind **Virtuoso** are some of the most advanced, and they combine to give very powerful and efficient support for real-time, DSP and parallel system design.

The ability to use any of the kernel services to access a kernel object located on another processor in the system, no matter where it is located, frees the programmer from considering the details of interprocessor communication. Because the semantics of the kernel services were designed for distributed operation, it is the only system that guarantees that the deterministic behavior of the application is unchanged when the target network is changed. This paradigm is called the **Virtual Single Processor**, as it allows a multi-processor target to be programmed exactly as if it were a single processor.

In the same context **Virtuoso** also provides multiple levels of support, allowing a trade-off to made of ease of programming for performance. Two levels

are dedicated to handling interrupts, one level consists of light context tasks (called the nanokernel processes) and the highest level is the preemptive priority driven C task level. This level has a rich set of semantics, is independent of the network topology and hence is fully scalable.

Despite providing these rich features, **Virtuoso** is still one of the smallest and fastest real-time operating systems available.

The latest addition to the family is **Virtuoso Synchro**, an application generator for synchronous dataflow applications. It supports the specification, simulation, emulation and implementation of mono- and multi-rate DSP applications on multi-processor targets, using a graphical user interface. The generated code runs with minimum of input-to-output delays and memory requirements, and can be used where even the smallest overhead from the kernel would be unacceptable

**Virtuoso** is complemented by a range of support tools and libraries that make **Virtuoso** a complete programming environment, designed to meet the needs of the developer in a wide range of applications. What **Virtuoso** delivers today is the potential to combine the incremental processing from a single processor to over a 1000 multi-processor network while meeting hard real-time constraints.

We look forward to receiving your comments, opinions and suggestions which might help us in the evolution of **Virtuoso**. As **Virtuoso** comes with 12 months support and upgrades, do not hesitate to contact us. It could save you a lot of time and it could start a long lasting relationship.

#### Milestones

- 1989: ISI founded

- 1990: Release of TRANS-RTXC

- 1992: Virtual Single Processor concept introduced

- 1992: RTXC/MP ported to the TMS320C30 and C40

- 1992: Release of 2nd generation kernel, Virtuoso

- 1993: Nanokernel programming level introduced

- 1994: Port to ADSP 21020 and 21060

- 1995: Release of Virtuoso Synchro

- 1995: ISI changed name to Eonic Systems, Inc.

### **Manual Format**

This manual set is divided into three distinct parts.

#### PART 1 Virtuoso Concepts

This part discusses the general philosophy behind **Virtuoso**. It gives information on how **Virtuoso** operates, the concepts behind its design and how the developer needs to use it. A short tutorial is included in order to prepare the user who is not familiar with real time programming.

#### PART 2 Virtuoso Reference Manual

This part contains the reference part of the manual with a detailed discussion of the way the **Virtuoso** kernel works, how to use the kernel services and how to use the **Virtuoso** development tools.

#### **PART 3** Virtuoso Binding Manual

Part 3 of this manual contains the specific information about installing and using a given **Virtuoso** implementation for a given target processor with a given C compiler. As this information may vary for different combinations of processors and compilers, the contents of this part depends on the particular combination you have licensed.

Other manuals include :

Virtuoso Technical Notes.

Virtuoso Modulo 0 - VI.

#### Manual Format

#### License agreement

**EONIC SYSTEMS** agrees to grant upon payment of fee, to the undersigned **CUSTOMER** and CUSTOMER agrees to accept a non-transferrable and non-exclusive license to use the Software, hereinafter referred to as the Licensed Product, as listed in the license registration form and subject license registration form is attached hereto and made a part of this Agreement. In case of doubt, the items as mentioned on the invoice upon delivery of the Software, shall be taken as the Licensed Product.

#### **OWNERSHIP AND CONDITIONS :**

#### 1. OWNERSHIP :

Customer acknowledges that Eonic Systems retains all rights, title, and interest in and to the Licensed Product and all related materials are and shall at all times remain the sole and exclusive property of Eonic Systems. The Licensed Product, the original and any copies thereof, in whole or in part, and all copyright, patent, trade secret and other intellectual and proprietary rights therein, are owned by and remain the valuable property of Eonic Systems. Customer further acknowledges that the Licensed Product embodies substantial creative efforts and confidential information, ideas, and expressions. Neither the Licensed Product nor this Agreement may be assigned, sublicensed, or otherwise transferred by Customer without prior written consent from Eonic Systems.

#### 2. FEES :

For and in consideration of the rights and privileges granted herein, Customer shall pay to Eonic Systems a license fee, due and payable upon execution of this Agreement, in the amount specified on the invoice.

#### 3. DEFINITIONS :

3.1 SOURCE CODE is any representation of the Licensed Product that is suitable for input to, or is produced as output from an assembler, compiler, interpreter, source translator, or disassembler, either directly or indirectly on any medium, regardless of type, including, but not limited to listings printed on paper, and any magnetic or optical medium.

3.2 EXECUTABLE CODE is any representation of the Licensed Product which can be directly executed by the instruction set of a computer or indirectly by an interpreter in a computer. The storage or transmission medium is not relevant to this definition and includes, but is not limited to, magnetic, optical, Read-Only-Memory of all sorts, and Random Access Memory. 3.3 OBJECT CODE is any form of the Licensed Product not included in the definitions of SOURCE CODE or EXECUTABLE CODE above including, but not limited to, object code files and object code libraries on any medium.

3.4 SITE is any single designated place of business where the Licensed Product will be used by Customer in the development of Customer's application. The SITE is limited to a single building or department or group of license users but Eonic Systems may, at its sole discretion, determine what shall constitute the SITE.

#### 4. CUSTOMER'S PRIVILEGES :

Regarding the Licensed Product, the Customer may :

4.1 Use any representation of the Licensed Product on one development station at the Customer's SITE.

4.2 Copy the Licensed Product for backup or archival purposes and to support Customer's legitimate use of the Licensed Product.

4.3 Merge or otherwise combine the Licensed Product, in part with other works in such a fashion as to create another work agreeing that any portion of the Licensed Product so merged remains subject to the terms of this Agreement. Whenever the source code of the Licensed Product is changed during the work, CUSTOMER shall consult Eonic Systems to verify if the changes are within the boundaries of the License Agreement.

4.4 Distribute on any medium the EXECUTABLE CODE derived from the Licensed Product so long as the Licensed Product is an integral and indistinguishable part of the EXECUTABLE CODE and the applicable runtime license fee has been paid to Eonic Systems.

4.5 Extend this Agreement to include more than one SITE by paying the appropriate license fee for the Licensed Product for each additional SITE.

4.6 Extend this Agreement to include more than one development station by paying an additional license fee for the Licensed Product for each additional development station.

#### 5. CUSTOMER OBLIGATIONS :

Regarding the Licensed Product, the Customer shall :

5.1 Include and shall not alter the Copyright or any other proprietary notices on any form of the Licensed Product. The existence of any such copyright

notice shall not be construed as an admission or presumption of publication of the Licensed Product.

5.2 Maintain appropriate records of the number and location of all copies that it may make of the Licensed Product, and shall make these records available to Eonic Systems upon reasonable request thereof.

5.3 Upon termination of this license, render written certification that all copies of the Licensed Product and any related materials, in any form, excluding EXECUTABLE CODE have been destroyed.

5.4 Take appropriate action by agreement or otherwise, with its employees, contractors, subcontractors, agents, or any other person or organization under Customer's control and having access to the Licensed Product, to satisfy Customer's obligations under this Agreement with respect to the use, copying, protection, and security of the Licensed Product.

5.5. Pay to Eonic Systems a runtime license fee for every processor or computer system executing any instance of the licensed product, be it as OBJECT CODE and indistinguishable from the EXECUTABLE CODE as far as the payment of said runtime license fees is not covered by any other agreement between Eonic Systems and CUSTOMER.

#### 6. CUSTOMER PROHIBITIONS :

Regarding the Licensed Product, the Customer shall not :

6.1 Permit any person or persons under its control to compromise the exclusiveness of the Licensed Product and the rights of Eonic Systems under the law of this Agreement.

6.2 Provide or otherwise make available to another party, any SOURCE CODE or OBJECT CODE or documentation which forms part of the Licensed Product, whether modified or unmodified or merged with one or more other works.

6.3 Use the benefits of the Licensed Product to engage in the development of a product or products having the equivalent functional specification or serving the same purpose as the Licensed Product so as to be in direct competition with the Licensed Product.

#### 7. LIMITED WARRANTY :

NO WARRANTY OF THE LICENSED PRODUCT IS PROVIDED EXCEPT AS STIPULATED HEREIN.

7.1 Eonic Systems provides the Licensed Product "As Is" without any warranty, expressed or implied, including but not limited to, any warranty of merchantability or fitness for a particular purpose.

7.2 Eonic Systems does not warrant that the functions contained in the Licensed Product will meet Customer's requirements, or that the operation of the Licensed Product will be uninterrupted or error free.

7.3 Eonic Systems does warrant the media upon which the Licensed Product is distributed to Customer to be free of defects in material and workmanship under normal use for a period of ninety (90) days from the date of shipment of the Licensed Product to Customer. Eonic Systems will replace such defective media upon its return to Eonic Systems.

7.4 Eonic Systems' liability hereunder for damages, regardless of the form of action, shall not exceed the amount paid by Customer for the Licensed Product. Eonic Systems will not be liable for any lost profits, or for any claims or demands against Customer. Eonic Systems shall not be liable for any damages caused by delay in delivery, installation or furnishing of the Licensed Product under this Agreement. In no event will Eonic Systems be liable for any kind of incidental or consequential, indirect, or special damages of any kind.

#### 8. GENERAL :

8.1 This Agreement is valid from the moment Customer has placed an order and Eonic Systems has duly executed it. This Agreement will remain in effect until Eonic Systems receives written notice of termination by Customer. Eonic Systems may terminate this Agreement, effective upon written notice thereof to Customer, if Customer neglects to perform or observe any of the terms set forth in this Agreement. This Agreement shall automatically terminate upon any act of bankruptcy by or against Customer, or upon dissolution of Customer.

8.2 If any of the provisions, or portions thereof, of this Agreement are invalid under any applicable statute or rule of law, they are, to that extent, deemed to be omitted.

8.3 This Agreement shall be governed by the laws of the State of Belgium and the relevant laws of the European Community and Customer expressly

submits to jurisdiction therein by process served by mail on Eonic Systems at the address below.

8.4 If Customer issues a purchase order, memorandum, or other written document covering the Licensed Product provided by Eonic Systems, it is specifically understood and agreed that such document is for Customer's internal purposes only and any and all terms and conditions contained therein shall be of no force or effect.

8.4 This Agreement supersedes any and all prior representations, conditions, warranties, understandings, proposals, or agreements between Customer and Eonic Systems, oral or written, relating to the subject matter hereof and constitutes the whole, full, and complete Agreement between Customer and Eonic Systems.

8.5. The Licensed Product includes a 12 months period of support and maintenance provided Customer submits his questions in written form and Customer duly returns the completed form to Eonic Systems that accompanies the Licensed Product.

#### RETURN A SIGNED COPY TO EONIC SYSTEMS TO VALIDATE THE 12 MONTHS MAINTENANCE

IN WITNESS WHEREOF

the parties hereto have executed this Agreement by their duly authorized representatives :

CUSTOMER (print)

Authorized Signature

Address (print)

EONIC SYSTEMS, Nieuwlandlaan 9, B-3200 Aarschot, Belgium.

Date

#### RETURN A SIGNED COPY TO EONIC SYSTEMS TO VALIDATE THE 12 MONTHS MAINTENANCE

| EXHIBIT A : LICENSED PRODUCTS : |           |        |          |  |  |     |  |  |

|---------------------------------|-----------|--------|----------|--|--|-----|--|--|

| P                               | roduct    | Serial | l Number |  |  | Qty |  |  |

| 1                               |           |        |          |  |  |     |  |  |

| 2                               |           |        |          |  |  |     |  |  |

| LICENSED SITE : (print or type) |           |        |          |  |  |     |  |  |

| Company                         | :         |        |          |  |  |     |  |  |

| Department                      | :         |        |          |  |  |     |  |  |

| Address                         | :         |        |          |  |  |     |  |  |

| State/Prov.                     | :         |        |          |  |  |     |  |  |

| ZIP/Postal                      | Code:     |        |          |  |  |     |  |  |

| Country                         | :         |        |          |  |  |     |  |  |

| Telephone                       | :         |        |          |  |  |     |  |  |

| Fax                             | :         |        |          |  |  |     |  |  |

| e-mail                          | :         |        |          |  |  |     |  |  |

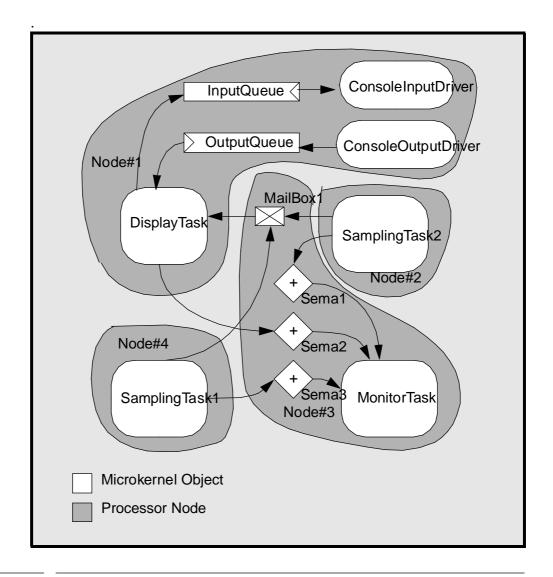

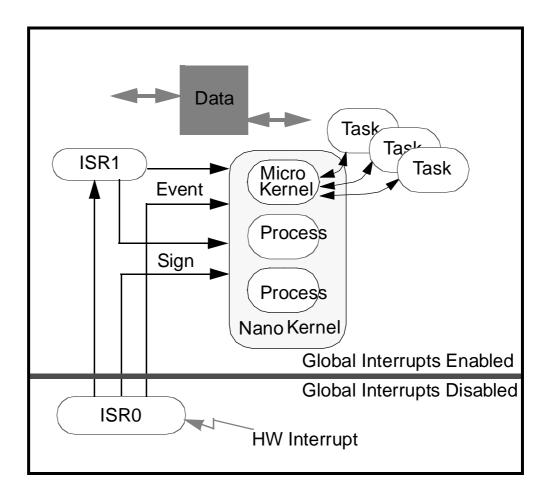

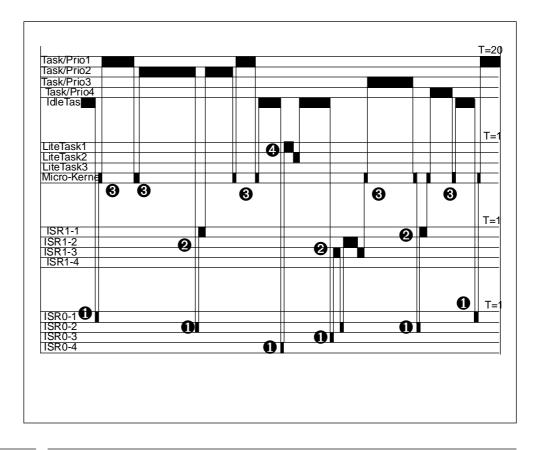

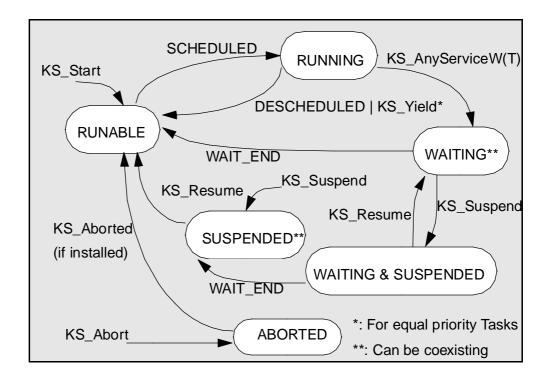

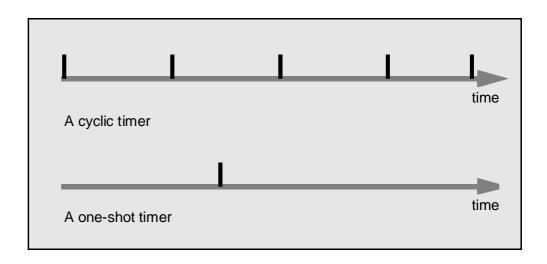

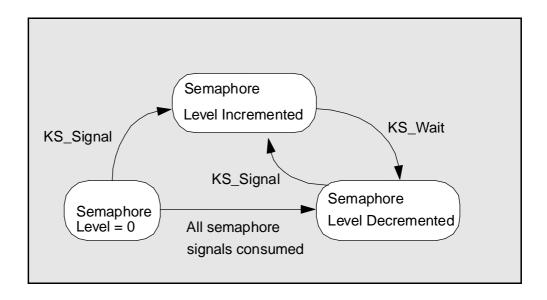

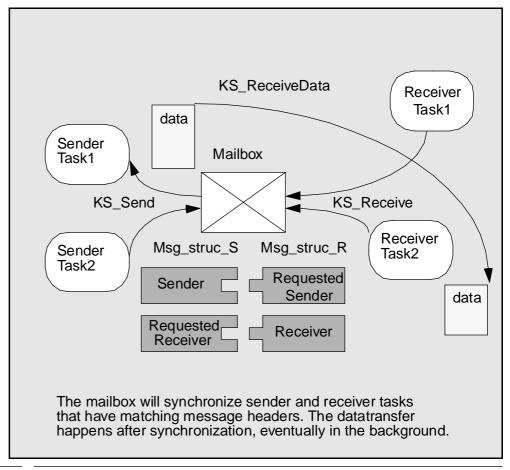

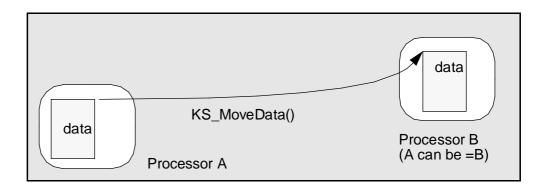

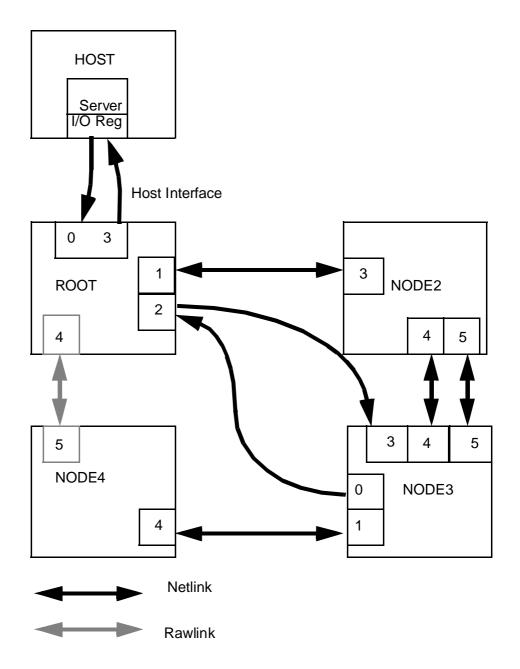

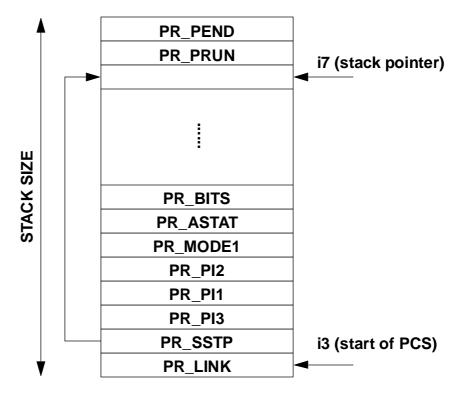

| Technical C                     | ontact:   |        |          |  |  |     |  |  |